By Peter J Mayhew

A dissertation submitted in partial fulfilment of the requirement of the University of the West of England, Bristol for the Degree of Master of Science

November 2011

Revision History

Rev Sections Affected Remarks

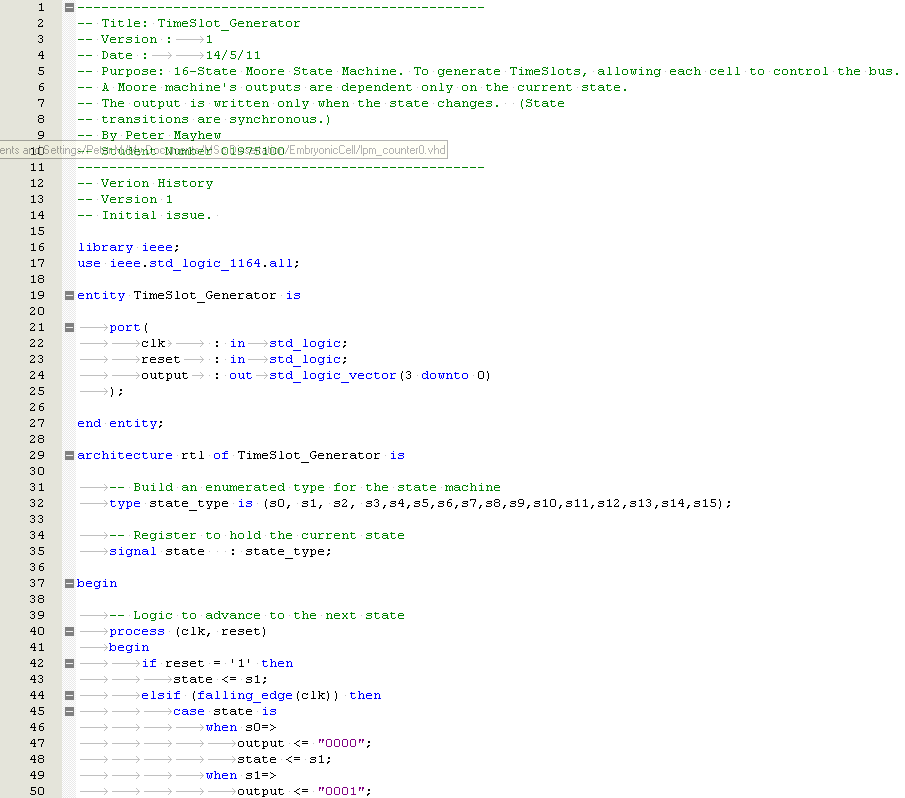

Issue 1 All Author: P. Mayhew

Date: 23/11/2011

Abstract

One of the growing concerns in avionics is Single Event Effects which can cause temporary data corruption on sensitive devices, such as FPGAs. Without mitigation, Single Event Upsets can cause undesirable effects, or worse catastrophic failure on avionic systems. This is especially the case at higher altitudes.

Several mitigation techniques are reviewed with evidence to suggest that combining multiple mitigation techniques such as TMR and memory scrubbing results in a system which is almost immune to Single Event Upset failure.

This dissertation presents research on Embryonic’s (Embryological Electronics) by studying the biological defence mechanisms of Eukaryote cells. The aim of this report is to develop a biologically inspired behavioural model in VHDL which can tolerate Single Event Upsets.

The behavioural model uses a cluster of embryonic cells in a cellular array which are configured by reading a configuration table (Genome). The Genome defines the functionality, timing, data path routing for each embryonic cell.

The study finds that the Genome successfully configures the cluster of embryonic cells to perform the function of a half adder. Using partial reconfiguration the cluster demonstrates fault tolerance against Single Event Upset.

Acknowledgements

University of the West of England

Frenchay Campus

Coldharbour Lane

Bristol

BS16 1QY

Supervisor: Nigel Gunton

Secondary Supervisor: Gabriel Dragffy

Introduction

Background

Aircraft systems are subjected to a wide range of environmental influences during their in-flight service. Therefore, before a system can be used for commercial or military flight a qualification unit is tested to an agreed specification by the stakeholders. This validates the unit can withstand agreed environments conditions. Typically, the types of tests performed on a qualification unit include, thermal, vibration, electromagnetic emission and electromagnetic susceptibility, lightning etc.

One of the growing concerns in avionics is the susceptibility of Single Event Effects (SEE) which impacts both the reliability and the safety of avionic equipment. Single event effects can cause temporary data corruption on sensitive devices such as Field Programmable Gate Array (FPGA) which if not mitigated can cause an avionics unit to produce undesirable effects, or worse catastrophic failure. Single Event Effects failures are difficult to diagnose since they only produce a temporary failure. Therefore, customer returned units may pass all tests and the technician may report no fault found. This is not desirable, as early life returns not only increases warranty costs, but also tarnishes the customer relationship. The purpose of this report is to research the effects of ionising radiation on aviation systems during flight. Also to review suitable mitigation techniques which can reduce the risks associated with single event effects and therefore improve flight safety and maintainability.

Product Justification

A customer requires a small displays navigation unit before the 2nd quarter of 2012. Deliverable must demonstrate fault tolerance against simulated ionised radiation.

Project deliverables

The project deliverables shall be defined by a high level Work Breakdown Structure (WBS). This defines the work and processes involved to execute this project, develop the project schedule. The WBS would normally show the resource requirements and costs, but this is out of scope for this project.

Figure ‑ Work Breakdown Structure

Project Aims and Objectives

The aim of this report is to develop a biologically inspired behavioural model in VHDL which can tolerate Single Event Effects.

The primary objectives are:

- Research ionised radiation. Discuss the reasons why this can impact the flight safety of avionic systems.

- Review and evaluate mitigation techniques to improve the system reliability against Single Event Upsets.

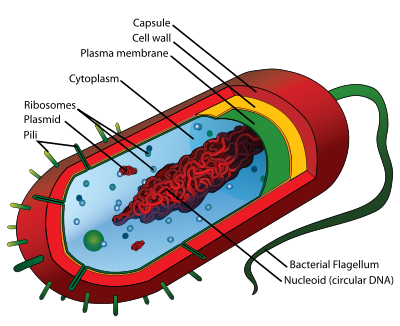

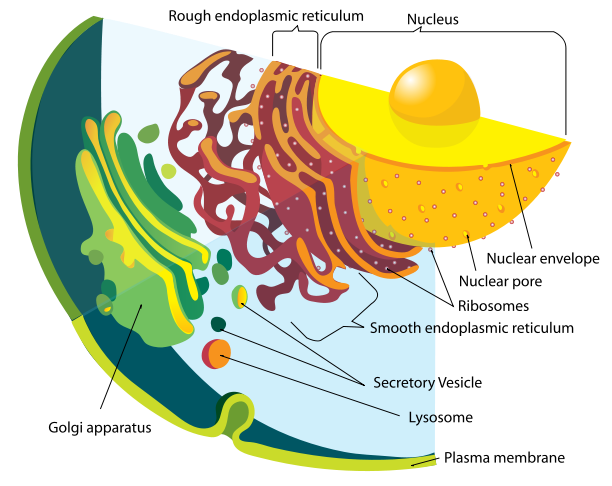

- Research Eukaryote and Prokaryote cells. Discuss the biological defence mechanisms.

- Design, develop, and synthesise a biologically inspired behavioural model in VHDL.

- Verify the biologically inspired behavioural model can configure as a half adder. Validate the functional correctness.

- Repeat objective 5 with a Single Event Effect. Verify the biologically inspired behavioural model reconfigures. Validate the functional correctness.

Project Planning Assumptions

- The project shall demonstrate fault tolerance by using a biologically inspired approach

- A VHDL behavioural model shall be produced as part of the project

- The project can be simulated, and no practical demonstration required

- Project shall start June 2010 and end November 2011

- Built-in self-test is considered out of scope for this project

- There is no access to a particle accelerator to generate ionised radiation. (Which would demonstrate the robustness of the design)

Constraints

Only 1x demonstration board available at the start of the project which uses the EP20K200EFC484-2X FPGA.

Quartus II web edition software package (Free software package)

Risk Analysis and Compliance

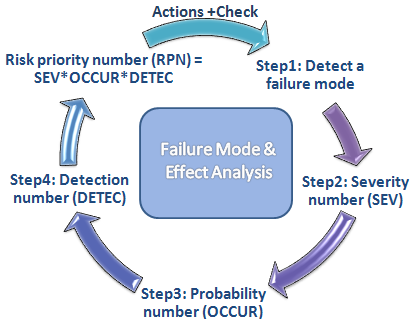

The risk analysis matrix and Compliance matrix, shown in Table 1‑1, is a scorecard that assess some of the potential risks in this project. Mitigation techniques explain how the risks will be avoided and the contingency plan can be used if the risk becomes un-avoidable. (10 high risk, 1 low risk)

|

Risk |

Probability/ Impact Score |

Mitigation |

Contingency |

Impact |

|

Minimal experience on biology. No experience on biological defense mechanisms |

7 |

Review other research papers and media to understand how biological cells work and their defense mechanisms |

Research only the required information on biological defense mechanisms |

Failure to understand and adopt a biological defense mechanism which could be implemented into a behavioral model. |

|

Simulated design may not function as expected |

9 |

Use a modular approach. Test and verify each part before merging into overall design |

Document that the design did not function as expected. Suggest an alternative method for future work |

Failure to demonstrate functionality of design |

|

Design may not prove to be fault tolerant |

6 |

Review more than 1 fault tolerance technique. Allow sufficient time review and compare solutions before implementing 1 into final design. |

Document that the design did not function as expected. Suggest an alternative method for future work |

Failure to demonstrate effectiveness of fault tolerance using the design |

|

Learning curve associated with tools to develop VHDL |

5 |

Allow sufficient time to develop the VHDL. Start early in the project |

Add process reengineering and additional CRP time to schedule |

Risk of delaying development and not reaching some milestones |

Table ‑ Risk Analysis And Compliance Matrix

Document overview

Section 2 : Overview of ionised radiation. How this impacts avionic equipment.

Section 3 : Reviews some of the common FPGA mitigation techniques used in industry.

Section 4 : Reviews biological cells to understand their defence mechanism.

Section 5: Design mythology for the embryonic VHDL behavioural model.

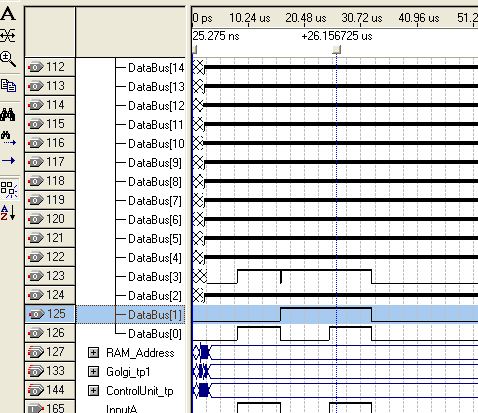

Section 6 : Verification tests performed on the embryonic cells.

Section 7 : Simulation and verification tests performed on the embryonic cells.

Section 8 : Conclusions which provide a discussion on the project outcomes, achievements, weaknesses, recommendations, future research, and personal reflection.

Appendix A : Project plan.

Appendix B : Supplementary Avionics Research.

Appendix C : Supplementary Biologic research including a breakdown of the eukaryote cells

Appendix D : Supplementary Systems Research including original VHDL designs, SEE types, Error detection techniques.

Appendix E Supplementary testing performed on the Embryonic Cells.

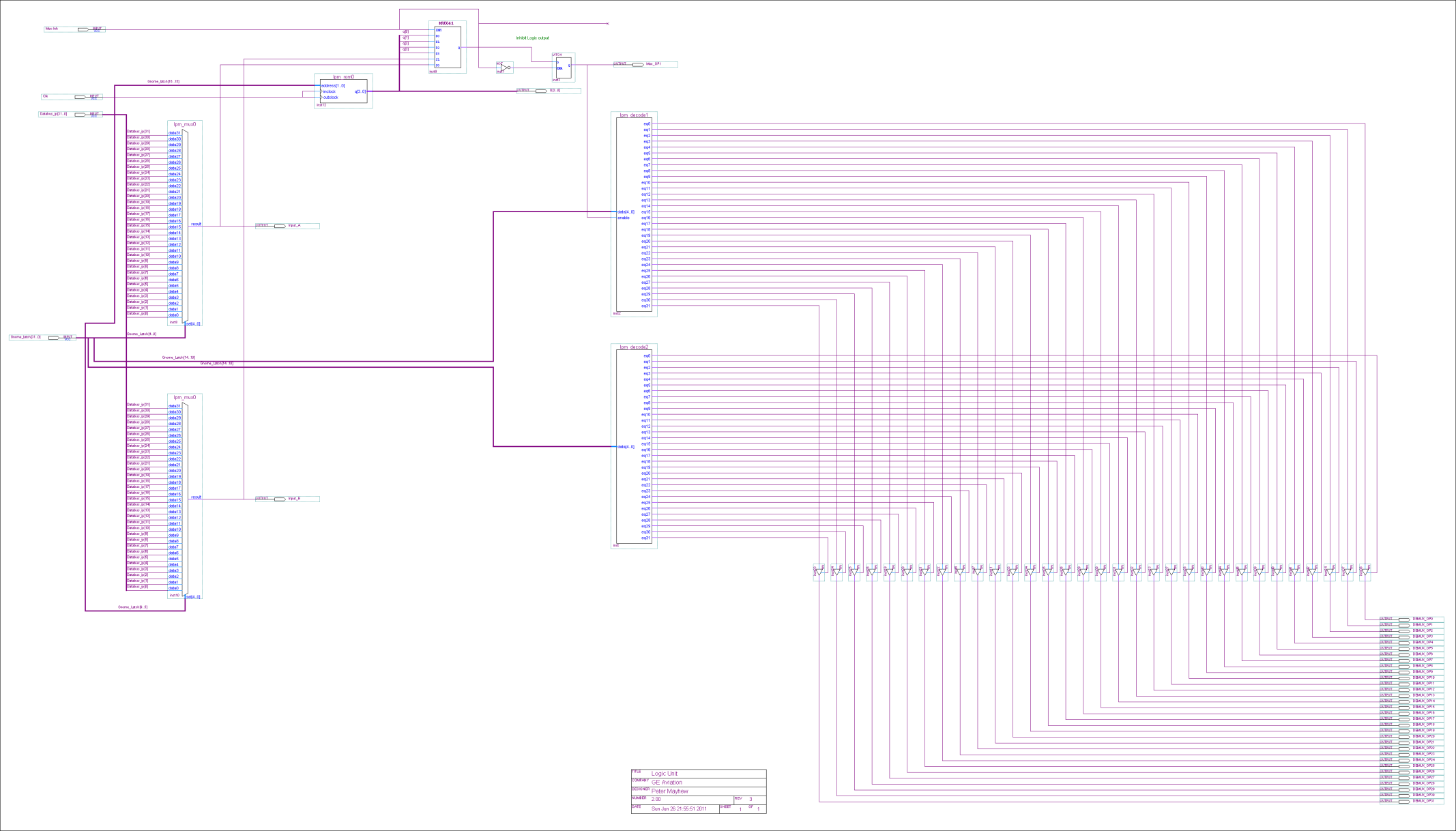

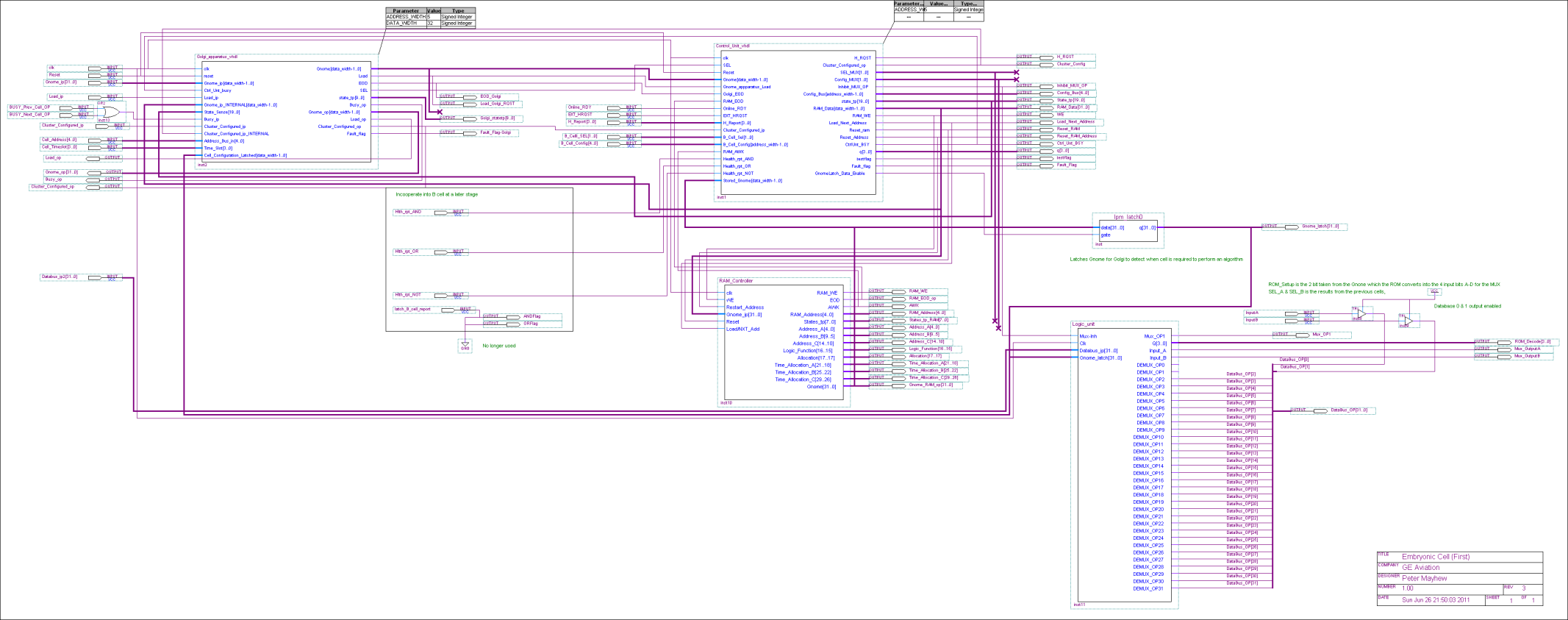

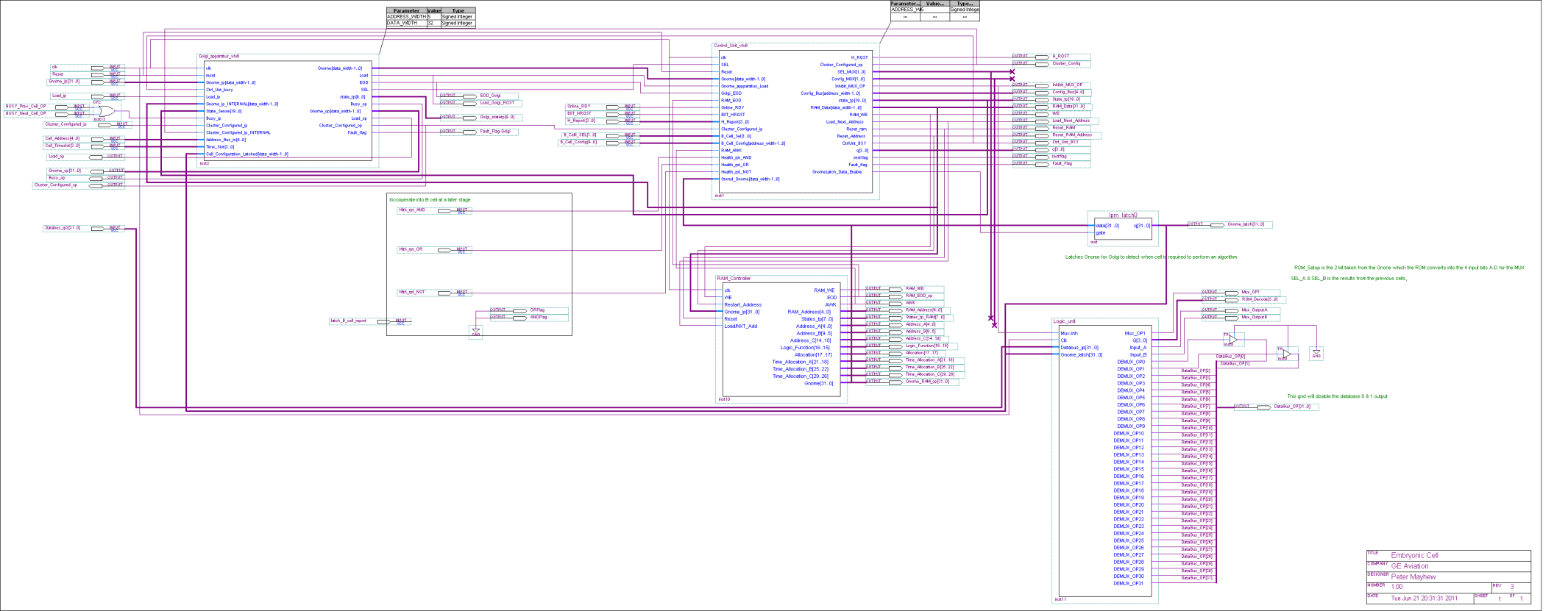

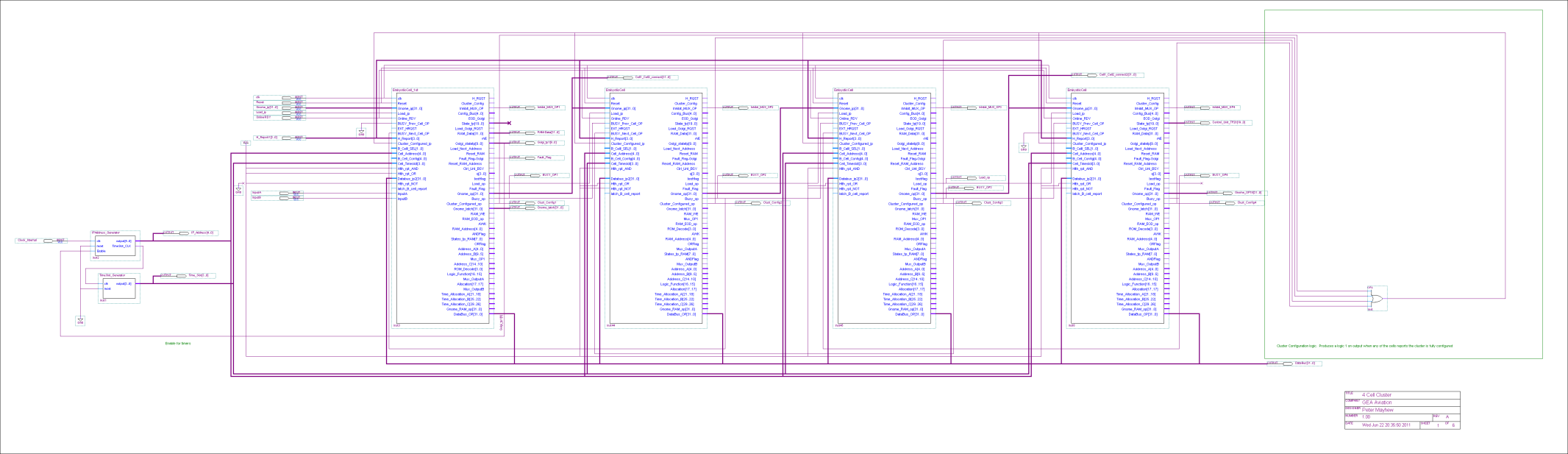

Appendix F : Circuit Diagrams for the Embryonic Cells.

Appendix G : Flow Charts for the Embryonic Cells.

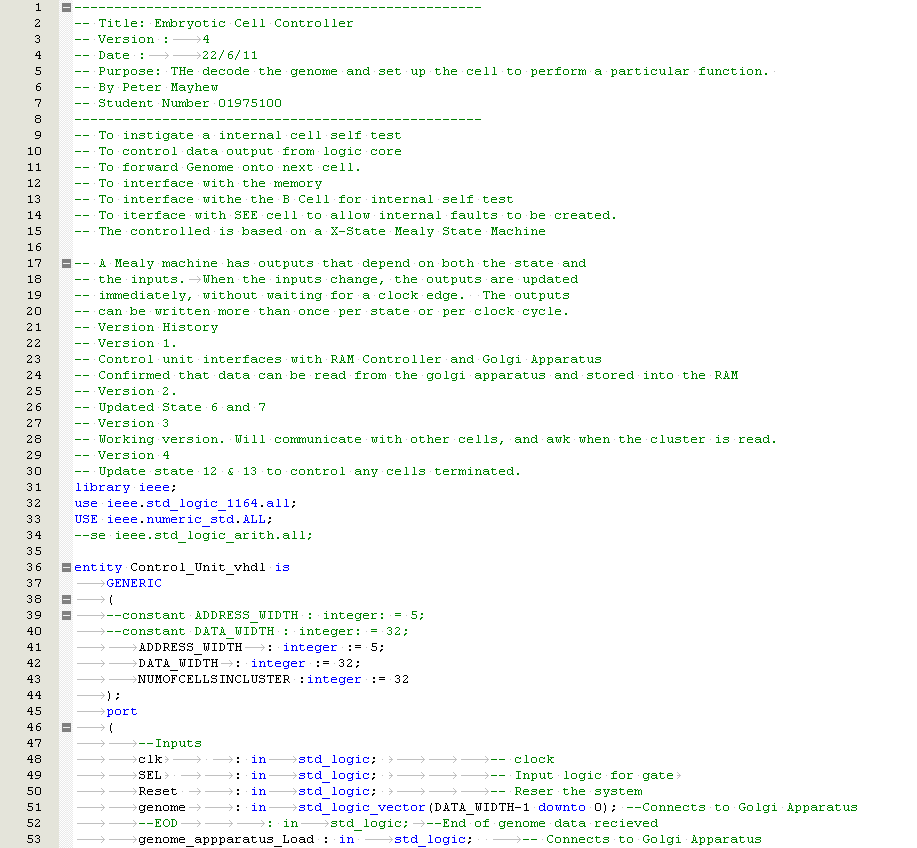

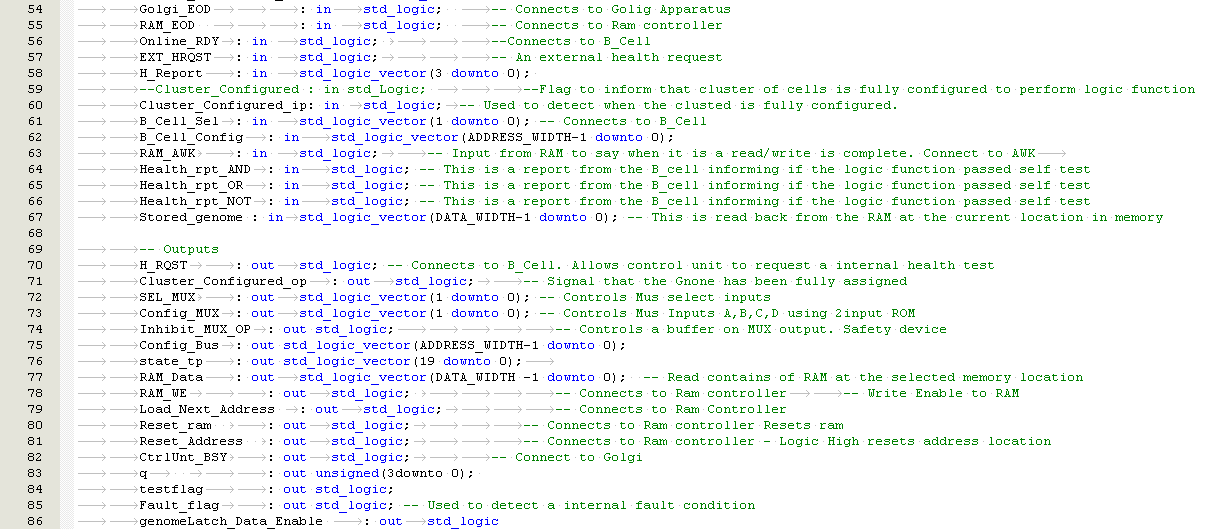

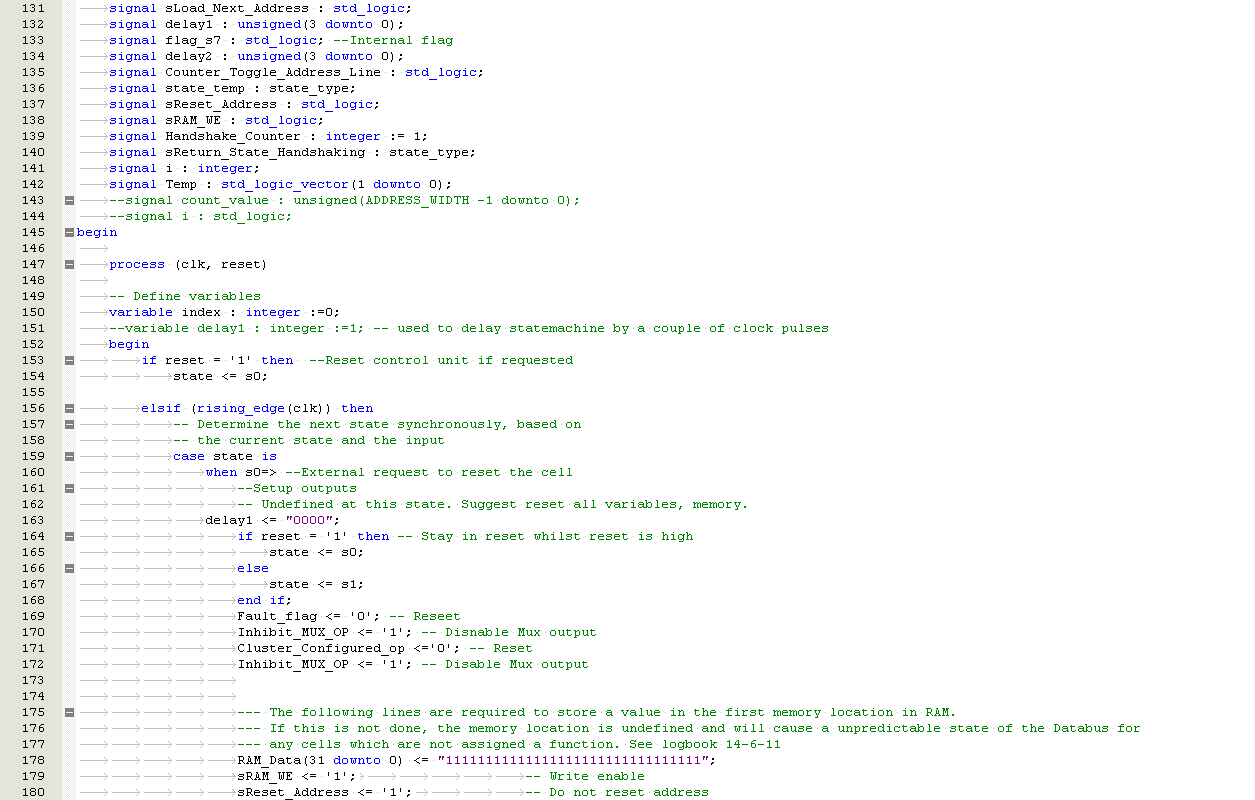

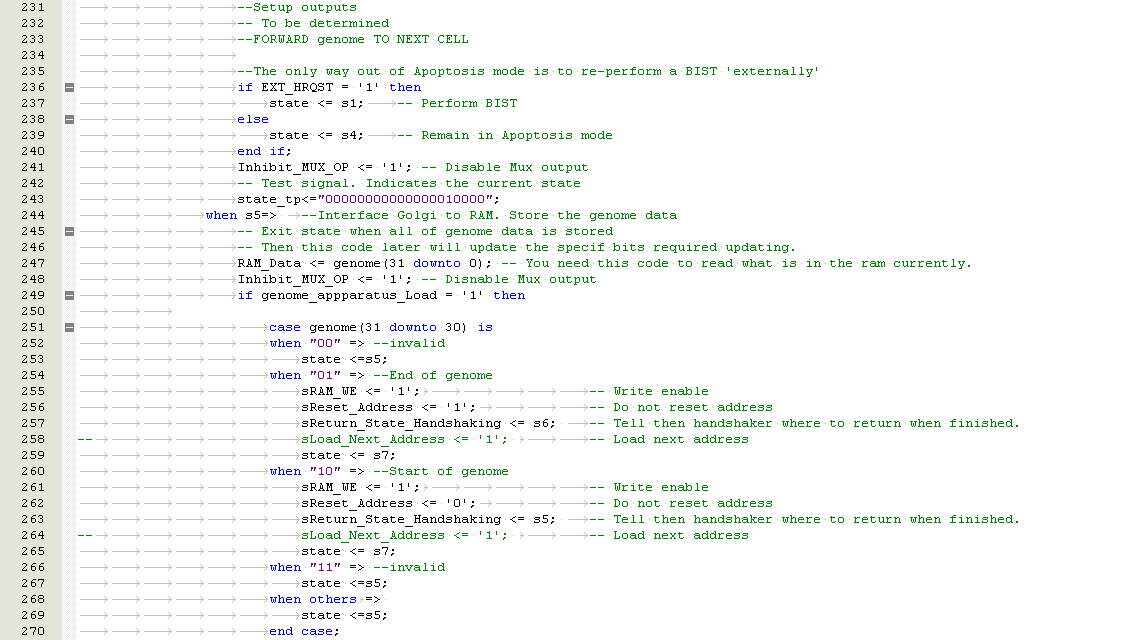

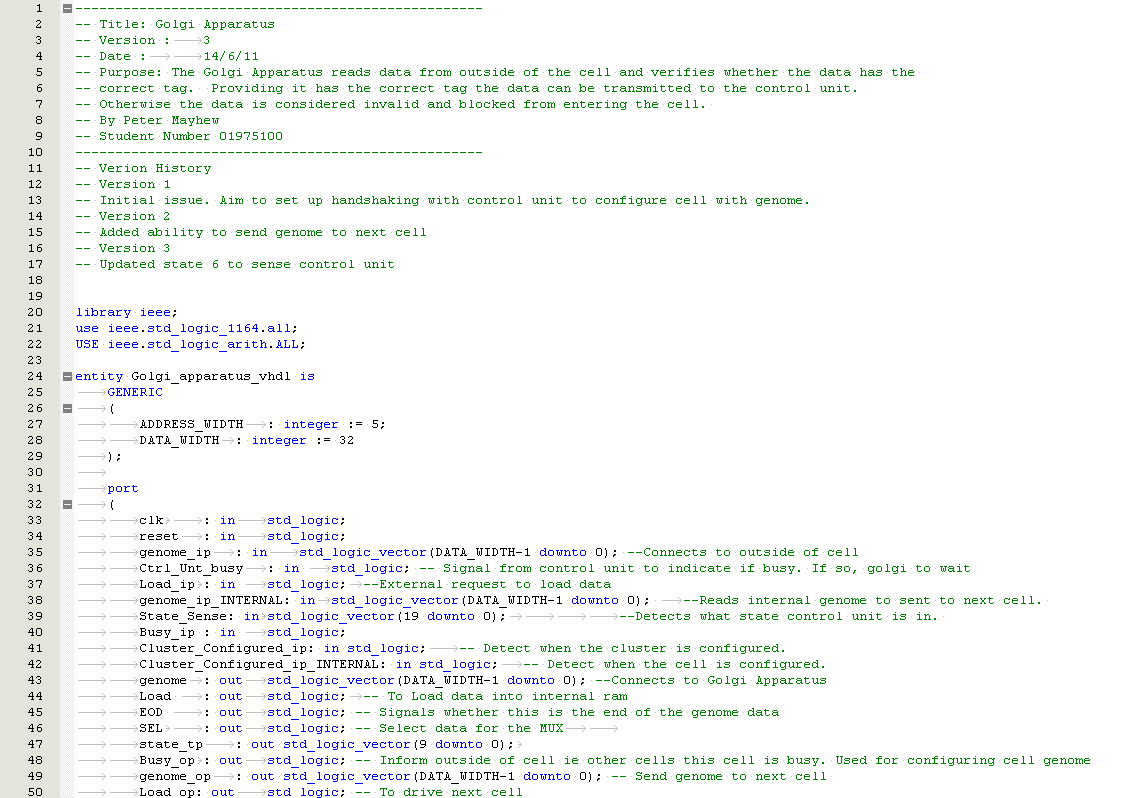

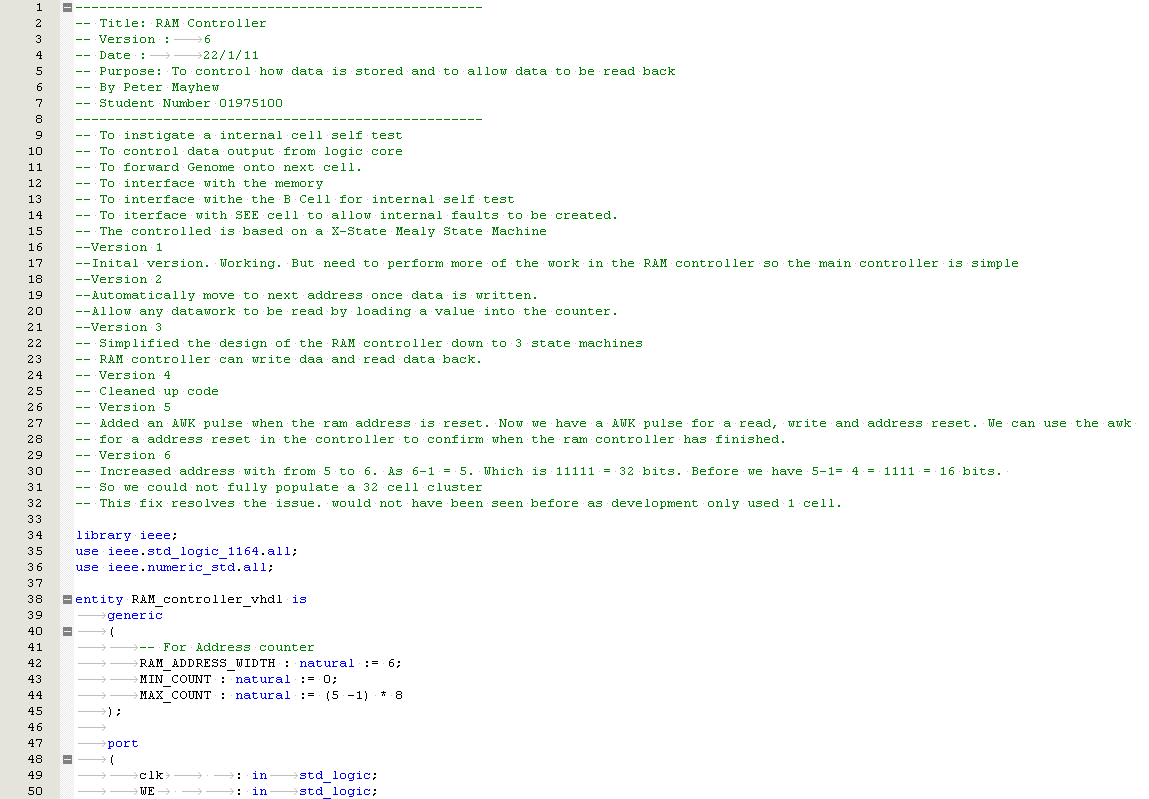

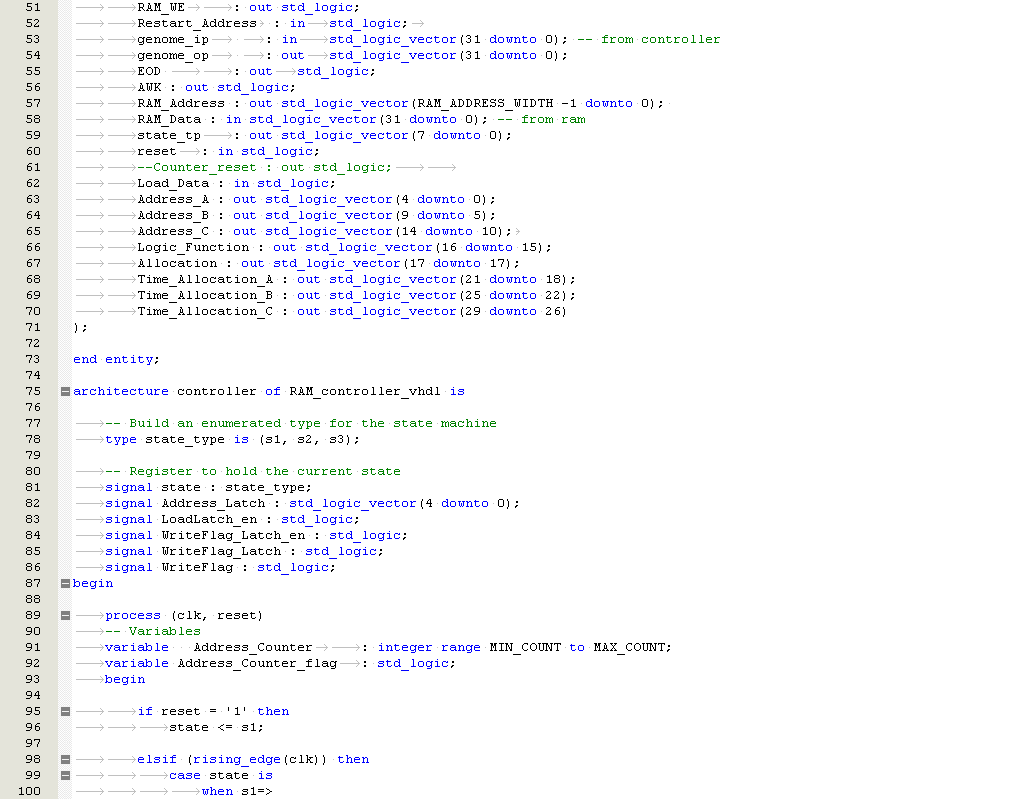

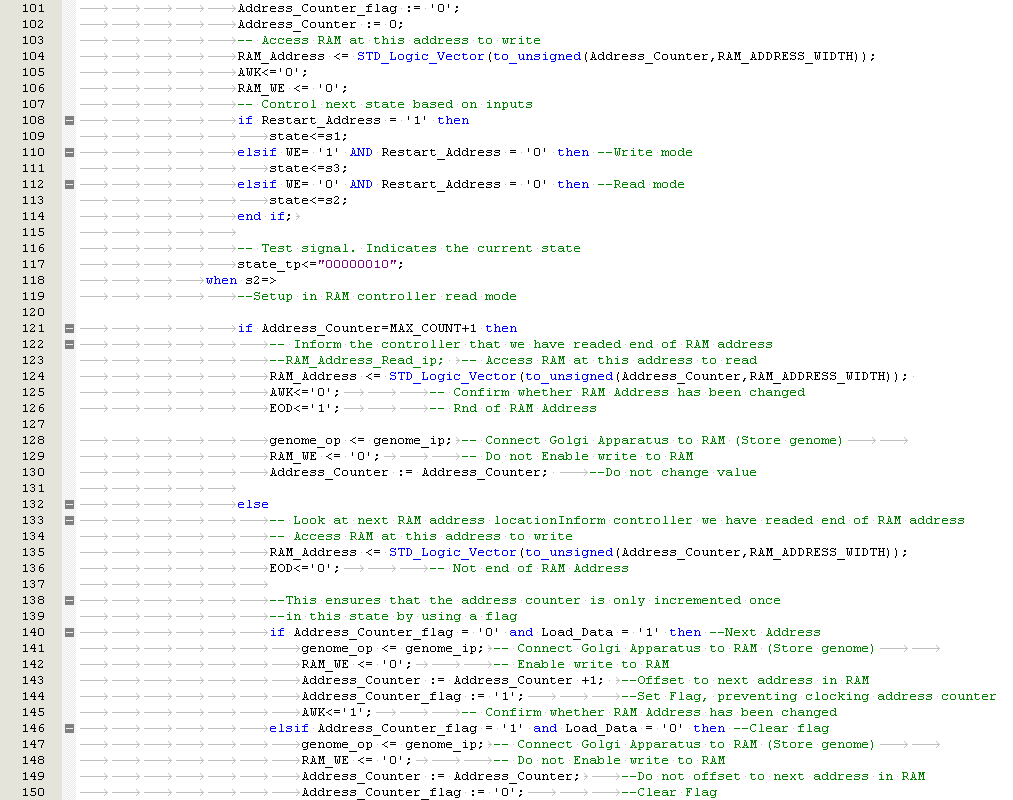

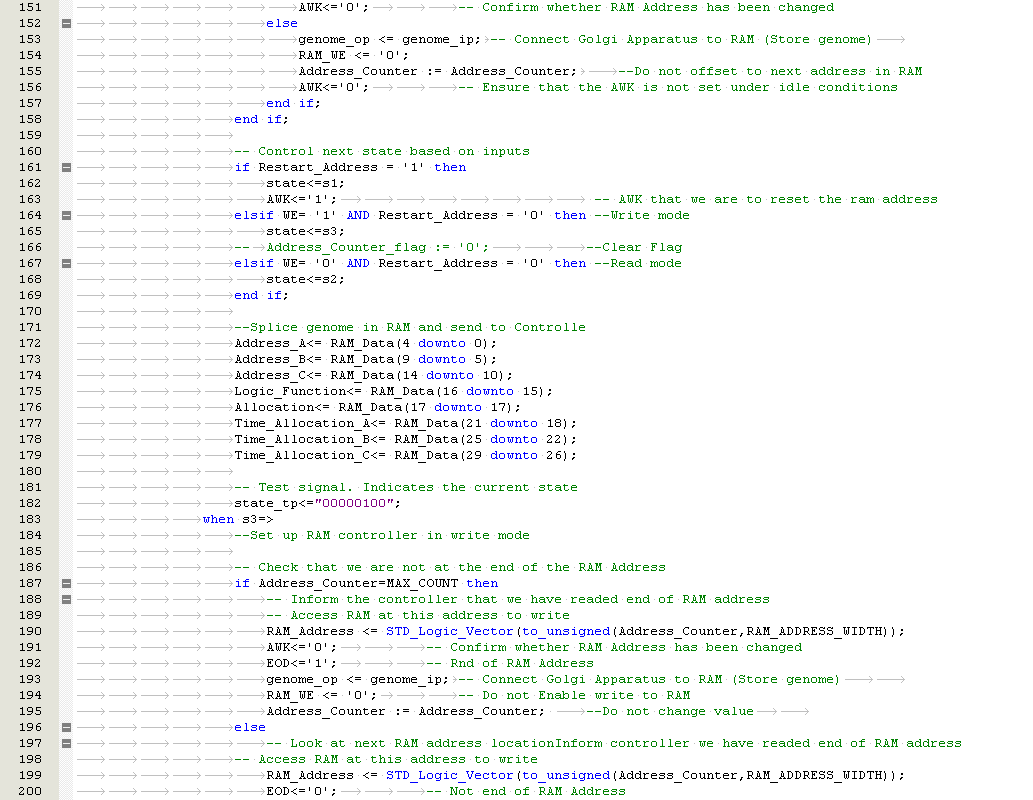

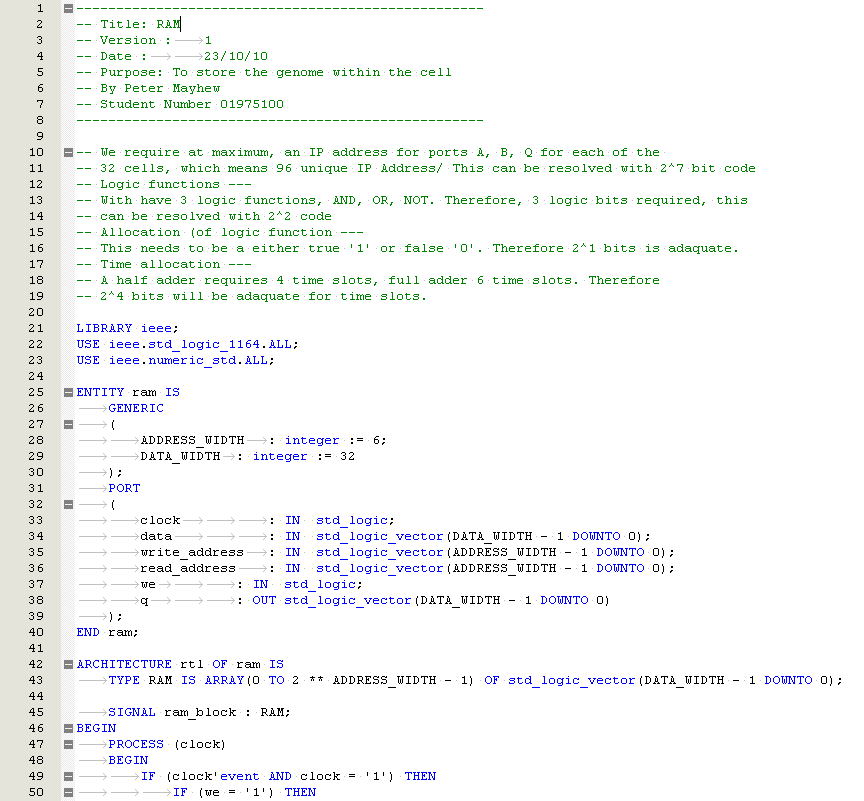

Appendix H : VHDL for the Embryonic Cell

Glossary

Ionizing Radiation: Any radiation, as a stream of alpha particles or x-rays that has sufficient energy to detach electrons from atoms or molecules.

Gray (Gy): The unit of radiation dose in the SI system. One Gy represents the absorption of 1

joule ( J) of energy by 1 kg of any material.

Sievert (Sv): The unit of radiation dose equivalent in the SI system.

Radiation dose: A way of describing the amount of energy transferred into a material that has been exposed to radiation. The unit of radiation dose in the SI system is the gray (Gy).

Rem: (obsolete): Equivalent dose is dimensionally a quantity of energy per unit of mass, and is usually measured in sieverts or rems.

Cosmic Radiation: The ionizing radiation that originates outside the solar system, a main source of which is thought to be exploding stars (supernovae).

Single Event Effect: Events caused by a single charged particle such as heavy ions or protons.

Prokaryote: An organism characterised by the absence of a nuclear membrane and by DNA that is not organized into chromosomes.

Eukaryote: A single-celled or multicellular organism whose cells contain a distinct membrane-bound nucleus.

Ionised Radiation and Flight Safety

The purpose of this section is to develop the readers understanding on ionised radiation which is followed by discussing the relationship between ionised radiation versus altitude.

Next, the impact of ionised radiation on electronics shall be reviewed which explains why Single Event Effects is a concern in the avionics industry. Finally, we shall review some of the mitigation techniques used in industry and how this impacts the systems reliability.

Ionised Radiation

Since the start of the 20th century there has been significant interest amongst the scientific community; to the unknown origin of radioactivity. This includes ionised radiation which was measured in all parts of the globe. It was the work of Professor Victor Hess who found that ionised radiation levels increased in proportion with altitude. Hess’s investigations showed that at 9,300m the radiation level were 40 times more intensive than on the earth’s surface (1) (2).

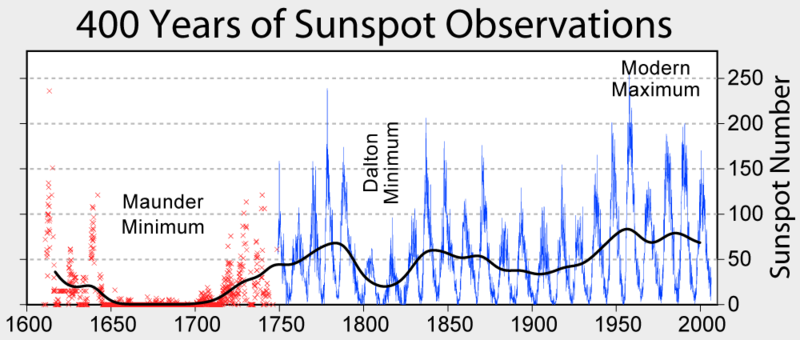

Natural occurring radiation has a number of sources such as cosmic rays from outside our solar system, charged particles from our Sun in solar winds and the radioactive decay of materials found in the earth’s environment (3). Since solar activity cycles about every eleven years it is possible for avionic systems to be exposed to an increased level of ionised radiation for duration of a couple of hours (4) (5). The reader might ask why not service the plane every ten-eleven years to coincide with this. One of the problems with ionised radiation is that some effects are accumulative and others are temporary.

Figure ‑ Sunspot Observations cycles every 11 years (5)

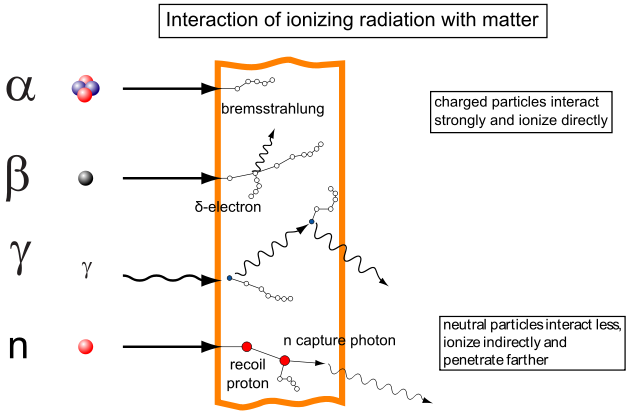

Ionised radiation is radiation which has sufficient energy to detach electrons from atoms or molecules and is found in the form of alpha particles, beta particles, gamma rays and x-rays, as shown in Figure 2‑2. Alpha particles (α) are positively charged and due to their large molecules and can be stopped by paper or skin. Beta particles () are electrons which can penetrate deeper than alpha particles, but can still be stopped by a thick layer of metal or water. Gamma rays (γ) and x-rays are known as electromagnetic radiation and can penetrate much further, even into lead and concrete (6).

Figure ‑ Types of Radiation (6)

In recent years there has been significant research by the World Health Organisation on the amount of atmospheric radiation the passengers and crew are exposed to during flight. One of the World Health Organisation programmes is The Radiation and Environmental Health Programme and this evaluates the health risk and public health issues in relation to occupational radiation exposure (7). The Federal Aviation Administration (FAA) Civil Aerospace Medical Institute have developed a system which gathers data from the Space Environment Services Centre of the National Oceanic and Atmospheric Administration (NOAA) which provides alerts on any disturbances on the Sun which could results in a high dose-rate of ionised radiation being subjected to the Earth’s atmosphere. Pilots respond to this alert by reducing the aircrafts altitude, and hence reduce radiation exposure (8). The FAA published the effective dose rates on aircraft from solar radiation is 30,000-60,000ft as shown in Figure 2‑3. This verifies that aircraft flying at higher altitude receive a higher effective dose rate of ionised radiation and therefore confirms the validity of Hess’s research.

Figure ‑ Effective dose rates from solar ionizing radiation at three altitudes on 20th January 2005 (9)

The research conducted by British Airways gives a reasonable indication of the ionised radiation levels present whilst their aircraft is in flight and is shown below in Table 2‑1.

|

Type of British Airways Aircraft |

Microsieverts per hour |

|

Concorde |

12-15 µSv |

|

Long haul aircraft |

5 µSv |

|

Short haul aircraft |

1-3 µSv [1] |

Table ‑ Measured Ionised Radiation Levels by British Airways (10)

Data collected from The World Health Organisation shows the estimated amount of radiation measured during flight, and is shown in Table 2‑2. The table has been expanded by calculating the microSievert per hour. This was achieved by divided the estimated radiation dose by the duration (hours).

|

Cosmic radiation dose on selected flights[2] |

|||||

|

Flight |

|||||

|

From |

To |

|

Duration (hours) |

Estimated Radiation dose (microSievert) |

Estimated microSievert / hour |

|

Sydney |

Singapore |

7.50 |

17 |

2.26 |

|

|

Bangkok |

Washington |

28.10 |

70 |

2.5 |

|

|

London |

Tokyo |

12.00 |

58 |

4.8 |

|

|

Buenos Aires |

Athens |

18.35 |

41 |

2.24 |

|

|

New York |

Paris |

7.00 |

35 |

5 |

|

|

Frankfurt |

Los Angeles |

9.50 |

51 |

5.36 |

|

|

Johannesburg |

Mumbai |

9.10 |

16 |

1.7 |

|

Table ‑ Cosmic radiation dose on selected flights [23]

Using the estimated radiation dose from Table 2‑2 we can calculate the arithmetic mean microSievert as shown in Equation 1.

Equation Average cosmic radiation reading by The World Health Organisation

The arithmetic mean was also taken from the British Airways results in Table 2‑1, and this has been calculated in Equation 2.

Equation Average cosmic radiation reading by British Airways

Based on this research, it would be reasonable to expect a reading between 3.41-6.66µ Sievert on average during flight. Whilst these results are useful, the reader might question why the results from two independent investigations differ. Upon further review, the author found the data from the World Health Organization had based its readings on “…cruise altitude of 10.000 m”; which equates to 32,000ft. However, Concord fly’s at 60,000ft. This would account for the radiation levels with British Airways being higher.

It is the same atmospheric radiation exposure on the aircrafts & crew effects can contribute to hard and soft faults in aviation equipment which commonly known as Single Event Effects (11).

Effects on Electronics

As a result of SEU, additional tests are required for commercial aircraft, military aircraft, and spacecraft to reduce the probability of failure. This is because a system failure on avionic equipment could result in the loss of human life or catastrophe. This can also result in high costs such as spacecraft which are very difficult to repair at long distances.

During take-off, the aircraft is travelling at low altitudes, so the electronics are less likely to be affected by the ionised radiation. Light aircraft and helicopters are less susceptible to the ionised radiation compared to commercial and military aircraft which generally fly at higher altitudes (12).

Electronics has been used in space exploration since the 1960’s and it was understood that the electronics needed to survive a much greater level of ionised radiation than equipment on the ground. Therefore, the electronics used space exploration applications were assessed for ionised radiation susceptibility and guidelines for their use developed (2).

During the 1970’s electronics were being used in safety critical functions on aircraft. Generally the components used were of military grade or internationally approved as this gave an independent assessment. However, in the latter years it became common practice for commercial parts to be used. As technology advanced, the complexity and lithography techniques resulted in higher IC density. During this time, it was not fully understood how these technological advances would also be a contributing factor to SEU susceptibility.

The research of SEU impacting aircraft was evolving from anecdotal incidents which had little scientific basis. Therefore, during 1988 and 1989 IBM flew a number of flight experiments using three aircrafts travelling over Seattle, Northern California, and Norway. Each aircraft was installed with a large array of 64k Static Random Access Memories (SRAM) and the number of SEEs on the SRAM was monitored. Later, IBM and Boeing were sponsored for a study by the Defence Nuclear Agency and Naval Research Laboratory. They used the data previously collected by IBM and the SEU’s monitored in a CC-2E flight computer on TS-3 E-3 military aircraft which flew mainly over West Coast. This study was completed in 1992 and demonstrated that SEUs in avionics was a scientific fact and that the in-flight failure rates correlated with the atmospheric neutron flux. These results also showed that the upset rates could be calculated using laboratory SEU data (13) (14).

By the 1990’s the geometric size of the silicon components had been significantly reduced. Some components were at risk of state change or damage since the induced charge from ionised radiation could exceed the critical charge of the component (2). As the manufactures used increasing amounts of memory per system it became an important factor for avionics to determine the SEE rate trends (15). It was during the 1990’s the first occurrence of SEU was observed and documented in avionics (2).

During 2000 the International Electrotechnical Commission (IEC) committee was formed as a worldwide organisation for standardisation comprising all national electrotechnical committees. The IEC published the Process management for avionics – Atmospheric radiation effects TS 62239 which was in circulation from 2003-2005 and then replaced with TS 62396-1 which is still used today.

Atmospheric Radiation Effects

FPGA’s are frequently used in avionic systems since they offer simplicity and flexibility during design. YANMEI (16) reports that the ability to improve a FPGA design avoids high non-recurring engineering costs. However, what YANMEI (16) fails to recognise is the extensive system testing and certification costs required for EASA or FAA approval[3]. Without this flight certification, the modification is not permitted to be used in airborne equipment.

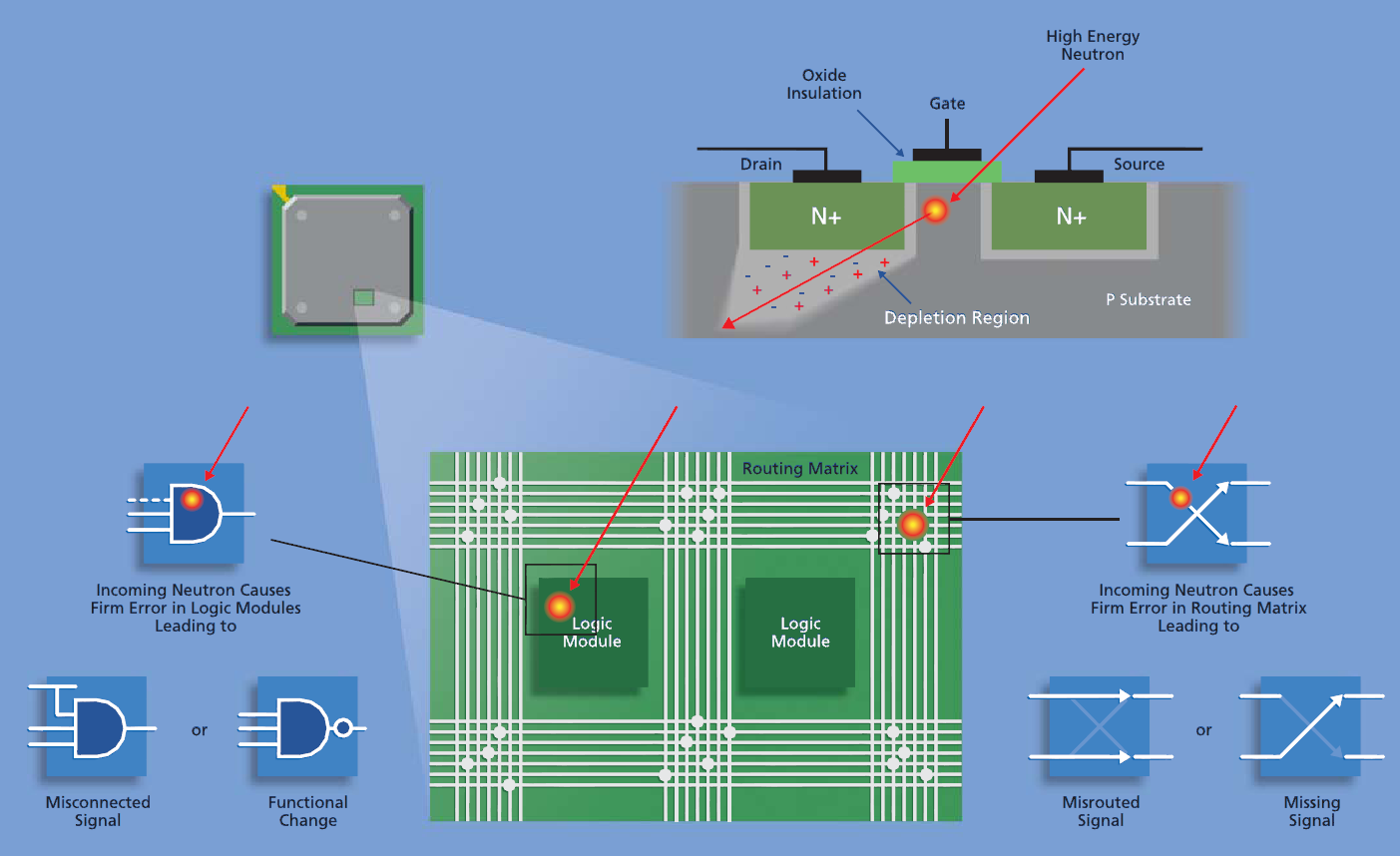

The interactions of ionised radiation with solid state devices such as FPGAs can cause ionisation in the semiconductor and create leakage current paths (17). If an ionised radiation particle collides with a CMOS device, the point of impact can potentially cause a transient change as shown in Figure 2‑4. The effect would depend on the function for that part of the circuit. For example, a memory cell could experience loss of information, which could lead to a system failure (18). Depending on the amount of ionised radiation, we could expect either permanent damage to the semiconductor, or momentary corruption of data.

The radiation effects on electronics can be categorised as either Lattice Displacement or Single Event Effect.

Lattice displacement

Lattice displacement is where the arrangement of the atoms in the crystal lattice is altered, and this can be caused by protons, neutrons, alpha particles, heavy ions and very high energy gamma photons (19). This damage is not temporary, as the crystal lattice, and hence the physical properties of the device are altered. This type of failure can be tolerated by using a FPGA which has radiation shielding. Dose-Depth curves can indicate the ‘stopping power’ or Bremsstrahlung of a variety of material thicknesses. Using this knowledge in combination with the FPGA radiation sensitivity will allow the engineer to develop a circuit which can tolerate its intended environment. The use of excessive shielding will increase the aircrafts weight. Therefore, the aircraft infrastructure should be assessed to determine which sensitive areas require radiation shielding. Studies have shown that whilst shielding is beneficial and reduces hazard caused by radiation, in some cases large thickness of shielding can worsen the effects. A heavy ion for example passing through though a certain thickness of material is slowed down to such an extent that its linear energy transfer and therefore its ability to produce ionisation are increased (20). The amount of ionising radiation on a medium is measured by Total Ionizing Dose (TID). This is the cumulative damage of the semiconductor lattice caused by ionising radiation over a period of time. The TID of the aircrafts life span should therefore be below the threshold of the weakest commercial device.

Figure ‑ Effect of a Charged Particle on a Semiconductor (3)

Single Event Effect

Single Event Effects (SEE) are events caused by a single charged particle such as heavy ions or protons impacting electronics. Shielding has minimal effect since the Beta and Gamma rays can still penetrate material as explained in paragraph 2.1 . SEE includes any measurable effect on a circuit due to an ionised particle strike. There are many forms of SEE such as:

- Single Event Upsets

- Multiple Bit Upset

- Single Event Functional Interrupt

- Single Event Latch-up

- Single Event Transient

- Single Hard Error

- Single Event Burnout

- Single Event Gate Rupture

This report will focus on discussing Single Event Upsets (SEU). However, the reader may read about additional types of SEE in Appendix D.3. SEU is a change of state caused by a high energy particle. For digital circuits this can result in a bit flip, such as changing Logic 0 to logic 1, or vice versa. A SEU does not directly cause the device to fail (hard error). Therefore, it is considered a soft error. This type of failure can be corrected with suitable error detection and correction (4). A system reset, or rewriting the memory data would also restore the device to a functional state.

The SEE failure rate of a component can be determined by the following equation (21)

λ = φ.σ

Equation

Where

λ = SEE Failure Rate (failures per device hour)

φ = Atmospheric Neutron Flux (n/cm2/hr)

σ = Device SEE Cross Section (cm2/device)

The neutral flux is standardised at a conservative 6000 n/cm2/hr which is derived from the typical conditions at 40,000 ft, 45° latitude and particle energies greater than 10MeV. This can be scaled for a given application (21).

Discussion

This section has discussed the relationship between ionised radiation and how it increases with altitude. The secondary research taken from British Airways and the World Health Organisation has also confirmed this relationship. This section has also explained the effects of ionised radiation on electronics which could be used on aviation equipment and completes objective 1 of this report

FPGA Mitigation Techniques

Aircraft electronics are subjected to a wide range of environments conditions such as thermal, vibration, radiation[4], lightning, fluid etc. Therefore, before any units can be certified for flight, they must pass qualification tests. This validates whether the product meets the stakeholders requirements.

Brogley (3) reports that radiation impact is often overlooked. This might have been the case for some organisations historically. However, there are now very tight guidelines for before equipment is certified for flight. Based on industrial experience, the author can confirm that ionised radiation testing is performed and there are procedural guidelines in place.

Traditional, vastly accelerated testing methods are used in industry for ionised radiation susceptibility such as

- Bombarding operating FPGA’s with Hess spectrum neutrons and high energy protons

- Los Alamos Neutron Science Centre (LANSCE) facility (http://lansce.lanl.gov ) and Crocker Labs http://crocker.ucdavis.edu/Site/

Ziegler (22) reports that the life testing of the FPGAs is slow process involving a tester which contains hundreds of chips and evaluating their failure rate costing about $300K / chip.

Another approach by Bargg (12) is to use the LANSCE facility to stimulate the effects of atmospheric radiation. This facility uses an 800-mega-electron-volt (800Mev) proton linear accelerator which provides beam current (23). Whilst Bargg (12) reports this is relatively in-expensive, he makes no claims of the costs involved. The rational for this difference in opinion between Ziegler and Bargg would be dependent on the size of the organisation, available budget and the type of testing required.

Another approach by Bargg (12) is to use the LANSCE facility to stimulate the effects of atmospheric radiation. This facility uses an 800-mega-electron-volt (800Mev) proton linear accelerator which provides beam current (23). Whilst Bargg (12) reports this is relatively in-expensive, he makes no claims of the costs involved. The rational for this difference in opinion between Ziegler and Bargg would be dependent on the size of the organisation, available budget and the type of testing required.

Figure ‑ LANSCE Linear Accelerator (23)

The author Ziegler (22) is quoted to say “Life testing at nominal conditions is very frustrating. For example, assume a tester which holds 500 chips which have an estimated SER of about 5000×10-9 fails/hr. This is a typical modern SRAM fail rate per chip. In order to get 50% reliability at two-sigma, you will need to wait for 16 fails or about 9 months. This means that the SER results will not be available until about a year after the first chips start coming out of the fabrication line.”

The author Ziegler (22) is quoted to say “Life testing at nominal conditions is very frustrating. For example, assume a tester which holds 500 chips which have an estimated SER of about 5000×10-9 fails/hr. This is a typical modern SRAM fail rate per chip. In order to get 50% reliability at two-sigma, you will need to wait for 16 fails or about 9 months. This means that the SER results will not be available until about a year after the first chips start coming out of the fabrication line.”

This type of testing is an empirically estimated approach using a Cyclotron which is a type of particle accelerator that uses high frequency AC. It should be noted this can only give us the statistical probability of SEE failure. An example of a Cyclotron is shown in Figure 3‑2.

However, this type of verification is outside the scope of this project. Therefore, a simulated test shall be performed for this report.

As previously discussed in paragraph 2.1 shielding has minimal effect on preventing ionised radiation. Even if a shield was used, it is reported by Ames (25) that it takes several feet of lead to block neutron radiation and this would be far too heavy to load on an aircraft. Also Bargh (12) reports that shielding is impractical as it takes around 3 meters of concrete to reduce neutron influence by 100 times. Since it is impractical to block the radiation other mitigation techniques will need to be explored.

This section shall discus some typical mitigation techniques used in industry to improve the reliability of FPGA’s used in avionic applications. We shall first review three methods to store data on FPGA’s and how they impact the robustness against SEU.

A typical situation for a manufacturer is a product improvement or a design fix which may result in a change to the FPGA firmware. This would typically be identified as a unit part number change for tractability and quality assurance. This allows a system to be reprogrammed without disassembly, reducing direct costs such as labour and preventing human error which could otherwise occur during disassembly / assembly of a unit. Bradley (26) states that the development and qualification costs of safety critical certified hardware is very expensive. However, with careful project management and planning the hardware can be re-used in other designs using a Qualification By Similarity report.

The Qualification By Similarity report is a way to justify to the customer that the hardware does not need to be re-qualified. For example the part might have already been qualified in a different project. Providing the customer agrees with the Qualification By Similarity report, a significant cost and time saving can be made.

Manufactures typically use one of three methods to store their programming data on the FPGA (27).

- Fuses or Antifuses: These FPGAs can be programmed once and use a high voltage to break, or make a connection between logical elements. These devices have high immunity to SEU in their configuration memory. However, because the registers and internal logic are not immune to SEU, the FPGA still requires fault tolerance in its logic design.

- EEPROM: These FPGAs use Electrically Erasable Programmable Read Only Memory EEPROM. As with the Antifuses, these FPGAs also suffer similarly with SEU.

- SRAM base FPGAs: Stores its configuration memory through Static RAM storage cells, which is susceptible to SEU.

Historically antifuse FPGA was used in appose to SRAM based FPGA because the logic is determined by antifuses which are considered to be relatively immune to SEU. However, SRAM based FPGAs have been of significant interest for aerospace electronic systems because they are reprogrammable (16).

SRAM based FPGAs have also gained huge popularity since they can be manufactured using cutting-edge fabrication technologies. This provides high logic gate density & low cost (27). These devices store their configuration data in the SRAM which is susceptible to SEU. If an ionised particle hits the surface of the SRAM within the FPGA there is a risk of bit flipping in the configuration memory from a logic 1 to a logic 0, or vice versa. This is known as a soft error in the industry and is not classed as permanent damage. (2) (16) (28). Normal behaviour can typically be restored by restarting the unit / over-writing the corrupted memory cells. If the radiation changes the configuration data stored in the SRAM cells, this could cause a AND gate being changed to a NAND gate for example. The original designed behaviour of the FPGA would therefore be changed (29), resulting in the incorrect outputs or for the unit to operate unexpectedly.

Effects such as latch-up can cause high operating currents of power transistors. This can result in degraded performance or destructive damage resulting in a potential system failure if not corrected. This is known as a hard error and this is illustrated in Figure 3‑3.

Figure ‑ Effects of Newton’s on SRAM FPGAs (30)

Another form of radiation which poses risk to FPGAs is alpha radiation. Brogley (3) raises concerns of alpha particles emitted from plastic moulding compounds which are used in semiconducting packaging. This is because the semiconducting die is within close proximity of the packaging. These alpha radiation particles are emitted by naturally occurring radioactive isotopes which are generated by impurities, primarily uranium and thorium in IC package moulding compounds. This is still an issue today despite the low alpha compounds used in the manufacturing process (3) (30) (31).

As FPGA fabrication advances for SRAM based FPGAs, there is a greater gate density for a given real-estate. By shrinking the transistor size, the charge required to switch the transistors also reduces. This increases the risk of the transistors being susceptible to radiation induced errors (27) (32). An example is Thelwell (4) who reports that SEEs for 64 to 256 Mbit devices range from approximately 6E-11 to 6E-16 upset/bit-hr at aircraft altitudes of 40,000ft.

FPGA Fault Detection and Recovery

Avionic systems susceptible to SEU failure will need to detect if a SEU condition has occurred. This prevents invalid data from being propagated through a system or stored in memory. Failure to detect corrupt data could result in a system failure. The preventative action is known to the industry as error detection.

Once the system has detected the error, it needs to be corrected to prevent an accumulation of errors. This can be achieved either by discarding the invalid data and replacing with valid data, which is known as error correction. Alternatively, the system could determine the correct data, which is known as Error Detection and correction. There are numerous published research papers which have discussed error detection and correction techniques for FPGA’s (26) (33). However, many of these methods require off-line testing which prevents the FPGA from processing (27). This is undesirable in critical avionic systems and therefore an on-line testing approach is required. On-line testing would allow the system to remain operating whilst the fault is being corrected.

A fault tolerant system requires four stages

- Detection of the error. To detect a SEU fault condition.

- Confinement of the error. To prevent the error from being propagated through the system causing further errors.

- Recovery of the error. Correct the error either by removal, or by error correction.

- Recovery of the system. Continuation of the system throughout this process without downtime.

Aircraft systems generally have Built-In Test (BIT) which allows the detection of faults, including SEE. However, BIT is only an effective mitigation strategy providing a large percentage of the system and critical components are checked. Also the BIT system needs to be relatively small compared to the overall system being checked otherwise Bargh (12) suggests a recursive scenario where a BIT may be required for the BIT system.

Dual Mode Redundancy

Dual Mode Redundancy (DMR) is available in a couple of variations, such as

- Hot spare. The spare module shadows the master module and takes control should the master fail.

- Double Resource with Reversion. Both master and slave modules are utilised simultaneously, yielding in improved throughput. A failure in one module will result in the system using reversionary mode. This mode has reduced throughput.

- Lockstep. This is where a redundant computer system executes its operations in parallel. The lockstep output can be used to determine if a fault has occurred.

DMR relies on Built-In Test (BIT) or data checking methods and cannot use a voting system. Therefore, DMR can only be used on avionics systems which are not critical, or if there is a backup system available (12).

Triple Modular Redundancy

Triple Modular Redundancy (TMR) is a fault tolerant design where three systems simultaneously perform the same task. Their outputs are compared by a voting system which produces a single output. The voting system can mask out a failed output preventing data corruption from propagating through the system.

When designing a complex system, some of the processes may not be critical, thus it may not necessitate TMR which is expensive, costing about 3.2 times the resource and a twofold increase in timing delays for a full TMR at a logic level (12).

Figure ‑ Detection Mitigation correction system (16)

An alternative option is to use selective TMR; whereby none critical parts of the design may only require duplex or single processors (34). Selective TMR would reduce the overhead and cost without significantly sacrificing reliability. However, this is an engineering decision. For highly critical applications where there is a risk of loss of human life or expensive machinery, Rennels (34) reports that it is likely that massive voting redundancy will always be used. This is based on the assumption that the modules will fail randomly and independently. Whilst this is plausible Rennels does not suggest using different designs for each module. This would reduce the probability that all the modules could fail simultaneously due to an inherent design flaw, and therefore improve the reliability of the system. It should be noted that TMR masks the individual error and cannot determine the cause of the error or correct the error. TMR simply ignores the outputs from the suspect FPGA (35).

Another disadvantage with TMR is that the voting system will introduce a delay into the signal. A paper by YANMEI (16) suggests a solution for systems containing a mixture of critical and none critical timing signals. For mission critical outputs where the signal cannot be delayed even for a short period, a majority voter would be suitable. A 3 state voter is suitable for none critical signals and this is shown in Figure 3‑4.

A three state voter is fed with the FPGAs outputs, and a control signal allows the 3 state voter output to go into a high impedance state. This prevents the corrupted data from propagating through the system. The advantage of a 3 state voter is the lower hardware overhead as this feature is inbuilt into FPGAs. A majority voter is the output voter which reflects the state of the majority of FPGAs outputs. In order for TMR to be most effective, each module should be designed and developed by different companies. This will reduce the probability of a design flaw being inherited in all three modules simultaneously, resulting in a system failure.

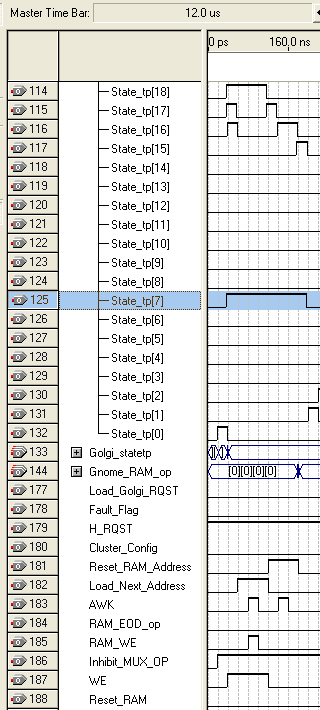

Interestingly, Yui (36) performed five tests with low upset rates. When TMR was used, there was a 25% reduction in functional errors observed. When partial reconfiguration was used, functional errors reduced by 40%. When both TMR and partial reconfiguration mitigations was combined there was no functional errors observed, as shown in Figure 3‑5. What this author has shown is that there may not be a single solution to SEU failure, and that we should consider a couple of mitigation techniques for the biologically inspired design.

![]()

Figure ‑ A comparison of frequency of errors to total runs for four possible [21]

The author Yui stressed that “it is however important that scrubbing was enabled, it was important to make certain the upset rate was less than the scrub rate. Overwhelming the test system with more upsets than it is designed to mitigate would produce misleading and erroneous data”

Partial Reconfiguration

Partial reconfiguration provides the ability to reprogram a portion of the FPGA whilst the rest of the FPGA continues to run without interruption (27). The system engineer will need to define which areas of the FPGA during the design phase that will be utilised for partial reconfiguration (35). In addition, the rate of scrubbing needs to be considered to prevent an accumulation of bit errors. A more detailed explanation of the type of scrubbing details can be found in Appendix D.4.4 to D.4.6.

Yui (36) reports that as the density of FPGAs increase, partial configuration will become more important for designers. This allows subsections of a FPGA to be reprogrammed whilst other resources within the FPGA are still running. The results taken from Yui (36) show when TMR is implemented into a design there was a 25% decrease in functional errors. When partial reconfiguration is implemented, functional errors decrease by 40%. When both TMR and partial reconfiguration are used in combination to repair configuration memory upsets as well as user logic upsets, there were no observed functional errors. Therefore, this report indicates that using either technique produces a marginal advantage to the design, however when both are used together the design was found to be immune to SEUs induced functional errors. In order to validate these results, further the experimentation would need to be repeated on a wider range of FPGAs. This would include those with higher density as our research shows these are more at risk to SEU.

Ryan Kenny (37) reports that partial reconfiguration can be beneficial to aerospace applications affected by SEU. However, Heiner (38) states that in order to take advantage of partial reconfiguration, the technique would need to be combined with data configuration scrubbing. However, as discussed previously, there is a conflict when using partial configuration and memory scrubbing techniques together. Therefore, this should be taken into consideration during the design phase.

Radiation Hardening

Radiation hardened FPGAs are based on commercial devices, with a variation to the manufacturing process and architecture. An example is using Silicon on Insulator (SoI) or Silicon on Sapphire (SoS), which is an insulating substrate in appose to a semiconductor. By changing the substrate of the FPGA it can be made less susceptible to ionised radiation. Whilst radiation hardening reduces its susceptibility to SEU, there are some disadvantages such as the relatively low demand compared to commercial devices. Therefore, the cost of radiation hardened FPGA can be prohibitively expensive and they often have significantly lower performance compared to Commercial-Off-The-Shelf (COTS) components (35) (29). Radiation hardened FPGA are antifuses or flash based, which results in reconfiguration limitations and generally smaller capacities compared commercial parts.

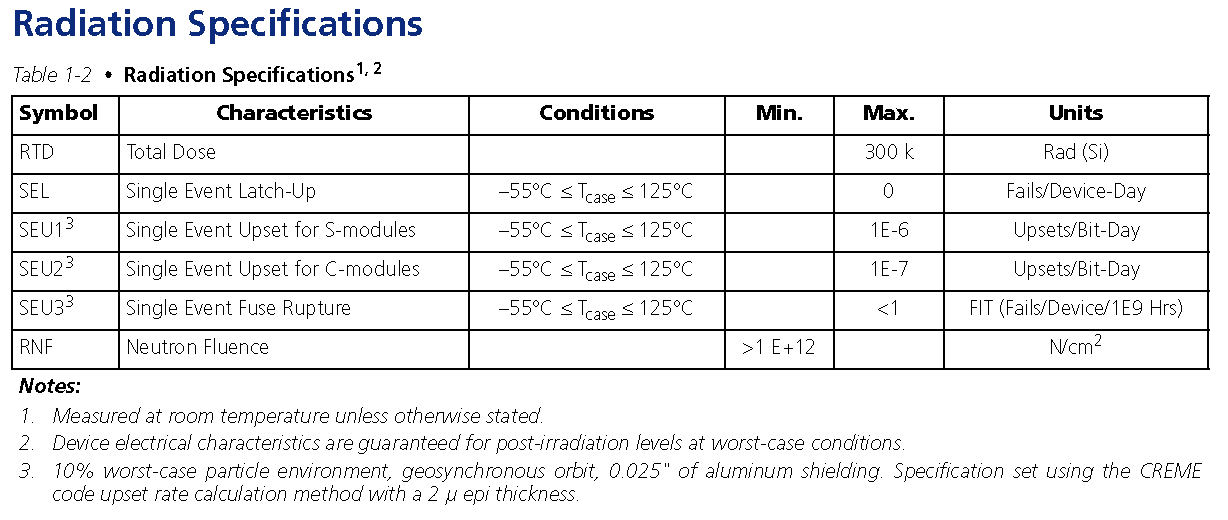

An Actel RH1020 radiation hardened FPGA was selected to determine its susceptibility to ionised radiation. An extract from the datasheet is shown in Figure 3‑6. This specifies a maximum total dose of 300K rad (Si). There is immunity to latch-up and less than 1×10-6 errors/bit-day.

Figure ‑ Actel Radiation Specification datasheet extraction (39)

A radiation report by Xilinx states that very few hard faults were detected during test, and that almost all faults were SEUs in the SRAM. No permanent faults were detected, and reconfiguration of the device was sufficient to regain full functionality after the occurrence of a SEU (16). Had the author Yanmei been more precise in his book to detail the tests more thoroughly, e.g. given details stating the radiation doses used, it would therefore be easier to make a more accurate comparison to the other experiments.

System Reliability

Since the reliability and safety of the avionics system can be affected by SEU, the safety standards needs to be considered. It might be the case that the system safety has already been assessed and based on its critical nature, without the effect of SEU, that triplex redundancy is required. However, if the reliability of the SRAM based FPGA is not within the Mean Time Between Failures (MTBF) then additional mitigation techniques will be required to lower the MTBF (40). In an ideal situation a system failure will result in a repair mechanism to restore the system to a functional state within a specific duration. The probability that a can perform a repair within a desired time is known as the maintainability of the system.

Maintainability M(t) is given by

Equation

Therefore, a relationship between maintainability M(t) and the repair rate µ

Similarly the Mean Time To Repair (MTTR) is given by the

MTTR=

Equation

The availability of a system is the probability that the system is function at any time, and is therefore defined as

Equation

Which can be rationalised to

where

Equation

Therefore, by reducing the MTTR the availability will be increased.

In order to restore system failure back to operation a repair is required. The probability that a system failure will be restored within x time is known as the maintainability of the system. The failure rate is defined as the number of failures per unit time as a fraction of the total population. This is normally expressed as a percentage failure rate per hour / per 1000 hours, or per year. There is a relationship between the maintainability and repair rate and the mean time to repair (MTTR). (20) (31)

Equation MTTR and relationship

MTTR and are related to maintainability M(t) by Equation 9 where t is the permissible time constraint for the maintenance action.

Equation Maintainability equation

For example a failure rate of 5% per 1000 hours and 10,000 components we have average of

The reciprocal of this tells us that the MTBF is

System Availability

The availability of a system is the probability that the system is functional according to expectations at any time during its scheduled working life.

Equation System Availability

This can be simplified down to Equation 11 since

In conclusion, a system with a reduced MTTR will allow for its availability to be increased and therefore a more reliable and economical system.

Discussion

This section has reviewed a number of mitigation techniques and there is evidence to suggest that combining multiple mitigation techniques such as TMR and scrubbing results in a system which is almost immune to SEU failure.

This section is concluded by recommending several design techniques to reduce the risk of SEU failure:

- Minimise the use of RAM and registers, due to their volatility with SEUs

- Combine more than one mitigation technique to improve SEU immunity

- Use radiation hardened components, budget permitting

- Finite state machined should be designed to not have redundant latch-up states which could be entered by an SEU

- Use “One Hot” or Gray code counters in appose to binary counters. This allows SEU’s to be detected by parity checks

This section has explored several mitigation techniques that could be used to improve the tolerability of flight equipment and therefore completes objective 2 of this report

Biological Cells

One of the aims for this report is to research how biological cells function and in particular how they can reproduce, reconfigure, and repair.

We shall first review prokaryotic and eukaryotic biological cells to understand their structure and functionality. This should provide some foundation biological knowledge to the reader. We shall then ask relevant scientific questions about how nature allows cells to self-repair and how this can be transcribed into a VHDL behavioural model.

Introduction to Biological Cells

The defence system in vertebrates has evolved over millions of years to what we call the immune system. The immune system has a layered protection system which identifies and kills bacteria and viruses. If a biological defence layer is penetrated then another layer will protect with more complex and ingenious barriers (26).

The human body consists of approximately 60 trillion cells (41), and each of these cells has a specific purpose within the body. The cell is the smallest unit of living matter that can exist on its own and is often referred to as the building blocks of life (42) (43). As part of human development and growth these cells multiple and divide forming.

Each of the 60 trillion cells contains a genome which is essentially a ribbon of 2 billion characters that is decoded to produce the proteins needed for the survival of the organism. This genome contains the genetic inheritance of the individual and the instructions for both the construction and the operation of the organism. The instructions of the 60 trillion genomes are performed simultaneously during the cells life span (44).

Each of the 60 trillion cells contains a genome which is essentially a ribbon of 2 billion characters that is decoded to produce the proteins needed for the survival of the organism. This genome contains the genetic inheritance of the individual and the instructions for both the construction and the operation of the organism. The instructions of the 60 trillion genomes are performed simultaneously during the cells life span (44).

The structure of Deoxyriboucleic Acid (DNA) is that of a long double stranded helix which consists of four repeating nucleotide bases Adenine (A), Cytosine (C), Guanine (G), Thymine (T). An analogy is that the chromosomes can be considered as letters. The letters in a particular sequence form words which are read on a page (45). It is the sequence of these nucleotides which creates the chromosome which results in the human genome cell.

The Meaning of Cells

It was the work of Robert Hooke in 1665 that used the word “cell” in his publication to describe the basic units of cork when viewed under a compound microscope. The biological word “cell” originates from the Latin word Cellula which means small room and is the smallest living entity in order to sustain life (46). The cell can be categorised as either a Prokaryotic or Eukaryotic.

All cells whether Prokaryotic or Eukaryotic have similar division progress (47)

- Replication of the DNA

- Segregation of the original and the replica

- Cytokinesis to end the cells division process

Fundamentally all cells in the human body are all identical and all contain the exact same DNA such as the lung cells execute a different segment of DNA then the skin (42). The exceptions are unfertilized eggs, and sperms which uses a different type of mitosis and only have one set of chromosomes, whereas the other cells in the body has two sets of chromosomes.

Next we shall discuss the difference between prokaryotic and Eukaryotic cells.

Prokaryote cells

Prokaryotes are a group of organisms. They are a self-contained living cell with an outer cell membrane which contains a cytoplasm fluid. The cytoplasm consists of fluids such as water, enzymes, amino acids and glucose molecules. Typical examples of prokaryotes cells are bacteria which are about one-hundredth the size of a human cell and invisible to the naked eye. Prokaryotes lack nuclear membrane so the DNA in bacteria cells is not protected. The prokaryote external membrane has long strands called Flagella which propel the cell. Flagella are not present in all bacteria, and the only human cells which have Flagella are sperm cells (46) (42) (48).

The word prokaryote derives from the Greek meaning Pro (Before) Karyon (Nut or kernel) and is illustrated in Figure 4‑2.

Figure ‑ Prokaryotic Cell Diagram (46)

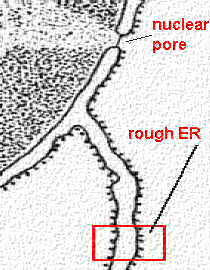

Eukaryote cells

A Eukaryote is an organism which contains complex structures within membranes. The Eukaryote cells have a nuclear envelope which contains the nucleus and this is the fundamental difference between a Eukaryote and prokaryote.

Eukaryote cells also contain other membranes such as mitochondria, chloroplasts and the Golgi apparatus. The word Eukaryote derives from the Greek meaning Eu (Good) Karyon (Nut or kernel) and is illustrated in Figure 4‑3. A more in-depth discussion of Eukaryote cells can be found in Appendix C.

Figure ‑ Endomembrane Diagram (46)

Cell DNA

The DNA contains the genetic information used for the development and functioning of the majority of living organisms. DNA is a nucleic acid and is organised into two long chromosomes. Nucleic acid is a macromolecule comprised of chains of monomeric nucleotides. These molecules carry genetic information of form structures within cells.

The chromosomes are duplicated before the cell divides, known as DNA duplication.

Cellular Repair

DNA is susceptible to mutation by Oxidizing agents, Alkylating agents, Electromagnetic radiation (such as ultra violet and x-rays) and DNA damage. Since DNA Damage and DNA mutation are fundamentally different (46), we shall discuss both to clarify their differences and how nature allows cells to self-repair.

DNA damage is physical abnormalities in the DNA such as single and double strand breaks in the helix. Providing there is redundant information available, such as undamaged DNA sequence in the complementary DNA strand, the enzymes can use a copy of the healthy DNA strand to repair the damaged strand. If the cell’s DNA remains damaged the transcription of the gene can be prevented and the translation into a protein blocked. Also the cellular replication process can also be blocked, as shown in Figure 4‑4 which results in the cells dying.

DNA mutation is where the base sequence of the DNA is changed and if these changes are not corrected the mutated cells could produce fault proteins (Ameno acids). A mutation cannot be recognised once the base change is present in both DNA strands. Therefore, as the cells replicate, so does the mutation.

Mutated cells which do not undergo a process known as programmed cell death (apoptosis) continues to divide are known as cancerous cells. Evolution has responded with two known DNA repair mechanisms which have been categorised as

1) Body enzymes directly repair DNA

2) Damaged region is removed and gap filled by DNA synthesis

Many cells communicate with each other by secreting chemical signals into the extracellular fluid. Some cells secrete regulatory molecules such as hormones and neurotransmitters into the blood stream using a process called trioxide. The chemical signals are targeted for distant cells. These signals perform functions such as growth regulation, development, and organisation. Due to technological limitations, it is currently not possible to implement such techniques into a VHDL behavioural model and is therefore outside the scope of this report. However, it is interesting to understand how nature as responded.

However, what we can learn from that human body is that it is capable of tolerating singular cell damage since the body is not solely dependent on a singular cell. Therefore, by designing the VHDL behavioural model using a cellular approach we can have confidence that the system will continue to operate even with multicellular failure.

Evolvable Hardware

A comparison of the defence system of the human immune system and the hardware protection of a FPGA is shown in Table 4‑1. Bradley (26) considers the atomic barrier and physiological defence mechanism to already exist with current SRAM based FPGAs. Therefore, we shall focus on the innate & acquired immunity mechanisms.

|

Defence mechanism |

Human immune system |

Hardware protection |

|

Atomic barrier (physical) |

Skin, mucous membranes |

Hardware enclosure (physical/EM protection) |

|

Physiological |

Temperature acidity |

Environmental settings (temperature control) |

|

Innate immunity |

Phagocytes |

N-modular redundancy Radiation Hardening Error Detection & Correction |

|

Acquired immunity |

Humoral immunity. Cellular immunity |

? |

Table ‑ Embryonic and hardware layers comparison (26)

The biological definition the innate immunity is one that provides immediate defence against pathogens. This is a defence which knows how to respond to a given situation. For example a TMR system has data corruption on the output, thus it ignores the outputs from the suspect module. Biologically, an acquired immunity is where the immune system has the ability to recognise and remember the pathogens. It is able to generate immunity based on its condition and develop greater defence against pathogens each time it is encountered. This is a significant step, from the innate immunity, and we need to evaluate how we can model this on silicon. The question is how can we recognise and remember SEU’s? Even if we can remember where the SEU’s occurred they are going to impact the silicon in random location and have a temporary effect. This raises the question whether remembering the SEU benefit the design, and it most probably does not. The problem with ionised radiation is that this is an external influence that can only be resolved by changing the material properties used, which is radiation hardening. It is not possible to grow new silicon, or to repair silicon with current technology (42). Therefore, our approach is limited to isolate and bypass the impacted area on the FPGA.

So to hypothesise, our body consists of 60 trillion cells, and damaging a couple of cells does not impact the body. So, the first step is to modulise the FPGAs design into self-contained cells. The FPGA also requires sufficient quantity of spare cells which can be used to replace faulty cells. An important consideration on deciding how the FPGA responds to a defective cell, and this is known as cell replacement.

Discussion

We have discussed the pathology of biological cells and reviewed some of the cellular defense mechanisms formed by nature. The research has demonstrated that the human body can continue to survive despite continuous cells dying or cells damaged/mutated due to

- Massive redundancy of spare biological cells

- Apoptosis (Programmed Cell Death)

- Redundant information (two copies of DNA strand)

It is not possible to grow new cells on the silicon. Therefore, this section concludes that the most appropriate biological defence mechanism that could be adapted into a VHDL behavioural model is n-modular redundancy. This can be achieved by including spare cells in the VHDL behavioural model design.

This section has researched both eukaryote and prokaryote cells with detailed understanding. Therefore, this completes objective 3 of this report

Next, Section 5 of this report shall discuss the embodiment of these defence mechanisms into an Evolvable Hardware approach.

Design Methodology

The development the biologically inspired behavioural model in VHDL is based on biological cells and is known as Embryonics (Embryological Electronics).

This section shall discuss the design methodology of the embryonic architecture which includes the design, synthesis, and implementation of the embryonic cluster.

Based on the research in Section 4, we have defined three defence mechanisms used by nature which could be embodied into an embryonic cell. These are:

- Massive redundancy of spare biological cells

Whilst massive redundancy of embryonic cells is not impossible, it is impractical. This is due to the silicon wafer having limited real estate and the limitations in lithography techniques. Of course, as lithography improves, this will allow more densely populated wafers, and as predicated by Moore’s law, the number of transistors is expected to double every two years. However, Moore’s law cannot continue indefinitely. As discussed in section 3.7 we should combine more than one mitigation technique to improve SEU immunity. Therefore, whilst allocating spare embryonic cells is a reasonable mitigation solution it should not be the only defence mechanism used.

In addition, unlike the human body, it is not possible to regenerate damaged silicon. Therefore, once all the spare embryonic cells have been used, any degradation will result in the design ultimately failing.

- Apoptosis (Programmed Cell Death)

Apoptosis is the process of Programmed Cell Death. This can be implemented in embryonic cells using a variety of self-test mechanisms available, as discussed in 0.

It is reasonable to suggest, that a cell failing self-test should be disabled. However, if the cell is still partially useable, then the cell could be allowed to perform specific functions which are not compromised by the type of failure. For example, an embryonic cell might not be able to perform a LOGIC AND function. However, if the cell can still produce the correct response for a LOGIC NOT function, then it would be reasonable to suggest the cell is still useable in the design and should be flagged as degraded and brought back online. This shall be discussed in more depth later in this section.

- Redundant information (two copies of Genome)

Finally, designing hardware with redundant information is once again only limited by the finite resources available on the silicon wafer. This technique shall be considered for the design of the embryonic cell by developing a Genome that contains the configuration data of the entire cluster and shall be copied to each cell. Whilst this will increase the amount of memory required on the FPGA, it will allow the biologically inspired design to more closely relate to the Eukaryote Cell.

Several research centres such as University West of England, University of York and Logic Systems Laboratory at the Swiss Federal Institute of Technology, Switzerland have developed Embryotic cells with fault tolerance. The University of York has focused on a POEtic model. This model was reviewed and outside the scope of the report. However for completeness, the reader may find an overview of the POEtic model in Appendix 0.

There was no existing embryonic VHDL behavioural model available in the public domain to build upon for this project. Therefore, the author decided to develop bespoke firmware specifically for this paper.

Before the embryonic cluster was designed, the following criteria was defined.

Embryonic Cell Criteria

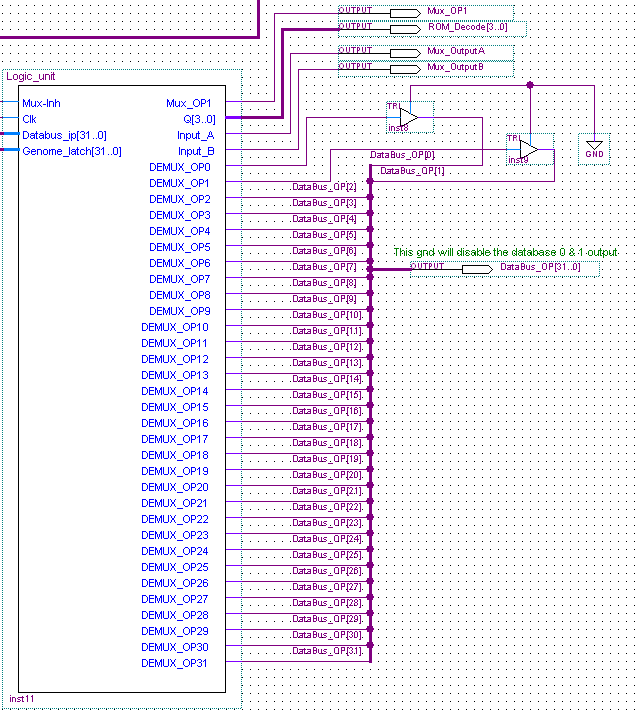

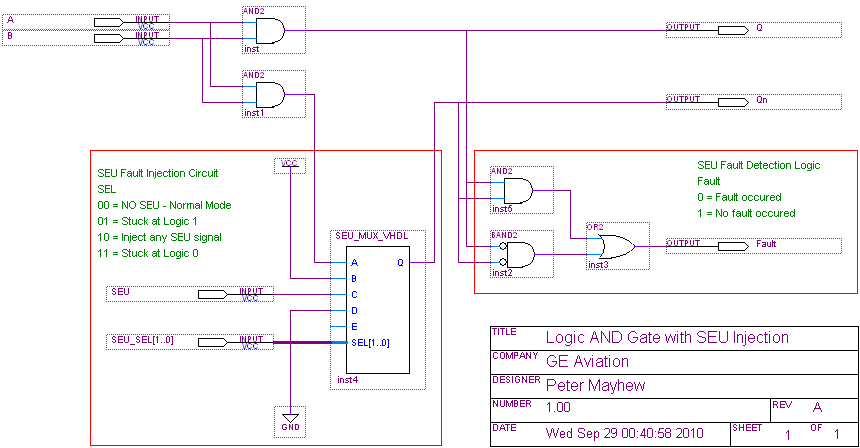

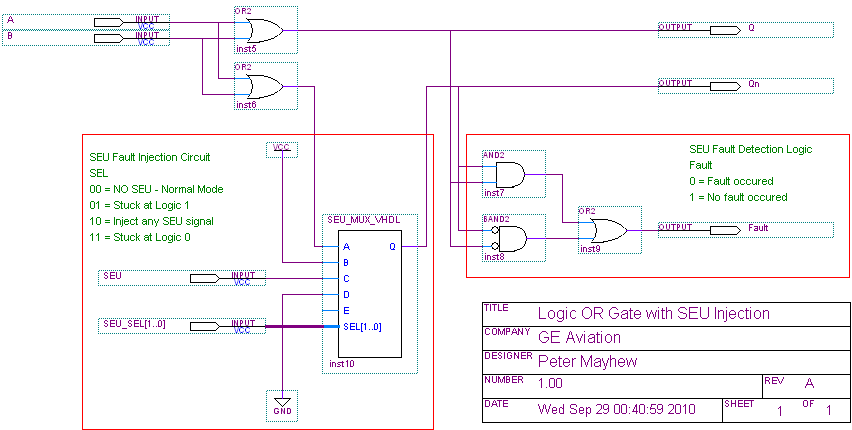

- Each embryonic cell shall have the capability to operate as a Logic AND, OR NOT gate

- It shall have the capability to perform the function of a half adder and product the correct logic response to a given input

- The embryonic cells shall have input to simulate a SEU fault condition

- A faulty cell shall be automatically detected and taken offline. The faulty cell shall not be used for the function whilst in a faulty state

- A faulty cell shall be automatically replaced by a spare cell in the cluster

- Each cell shall have internal memory to store the Genome

- Each cell shall have the ability to automatically access, store and retrieve any part of the Genome without any external input

- Each cell shall provide test outputs such as state number, faulty signals to permit cell diagnosis

- The cluster shall have a minimum of 12 cells

Embryonic Cell Constraints

- The design shall use a EP20K200EFC484-2X FPGA

- The behavioural model shall have a maximum of 8320 logic cells. (Limitation of FPGA used in project)

Brainstorming Biological Cells & Embryonic Cells

During the project, a brainstorming exercise was used to evaluate both the biological and eukaryotic cells. This was first used to understand the make-up of the biological cells, and then how this can be modelled in a VHDL behavioural model. The results from this brainstorming are shown in Figure 5‑1 & Figure 5‑2.

Figure ‑ Brainstorming for Biological Cells

Figure ‑ Brainstorming to Eukaryotic Cells

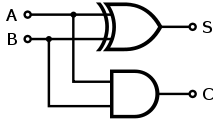

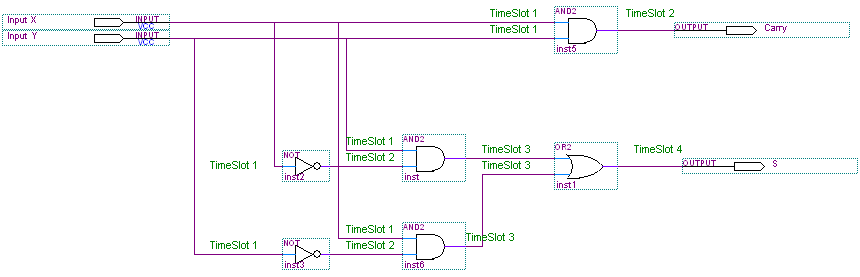

Half Adder

The Half adder shall be reference throughout the remainder of this report, so we’ll quickly review the basic principles of what a half adder does.

Electronic devices such as calculators are capable of performing very complex operations which is built on basic arithmetic, such as the addition of numbers. For example multiplication (4*3=12) is the same as adding multiple copies of the same number together (4+4+4=12).

A half adder adds two 1-bit binary numbers A & B together to produce two outputs S and C which are called Set and Carry respectively.

Whilst the half adder does allow for a carry out (C) it does not have the ability of carry in. If a carry in was required, then a Full adder should be used. The half adder truth table is shown in Table 5‑1. A half adder can be designed using one exclusive Logic OR gate, Logic AND gate as shown in Table 5‑1. The half adder shall be used later in this report to demonstrate the functionality of the embryonic cells operating together.

|

Input |

Output |

||

|

A |

B |

Set (s) |

Carry (C) |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Table ‑ Half Adder Truth Table

Figure ‑ Half Adder Logic Diagram

Real-Time Fault Recovery

A system is defined as being real time if it depends on logical correctness and temporal correctness. Tyrrell (49) states that the first principle of fault recover is that “no fault recovery method can be legitimately proclaim efficacy until it is proven to be both logically and temporally correct.” Tyrrell further explains that:

Logical correctness is when the system performs all its assigned tasks and functions according to specification without failure.

Temporal correctness means the system is guaranteed (repeatedly) to perform these functions within explicit timeframes. However, it is outside the scope of this report to develop an embryotic cluster which addresses the temporal correctness. There are two recommended methods to ensure temporal correctness which are: Redundancy and or Multiplying the clock frequency.

Partial Reconfiguration using Embryonic Cell Redundancy

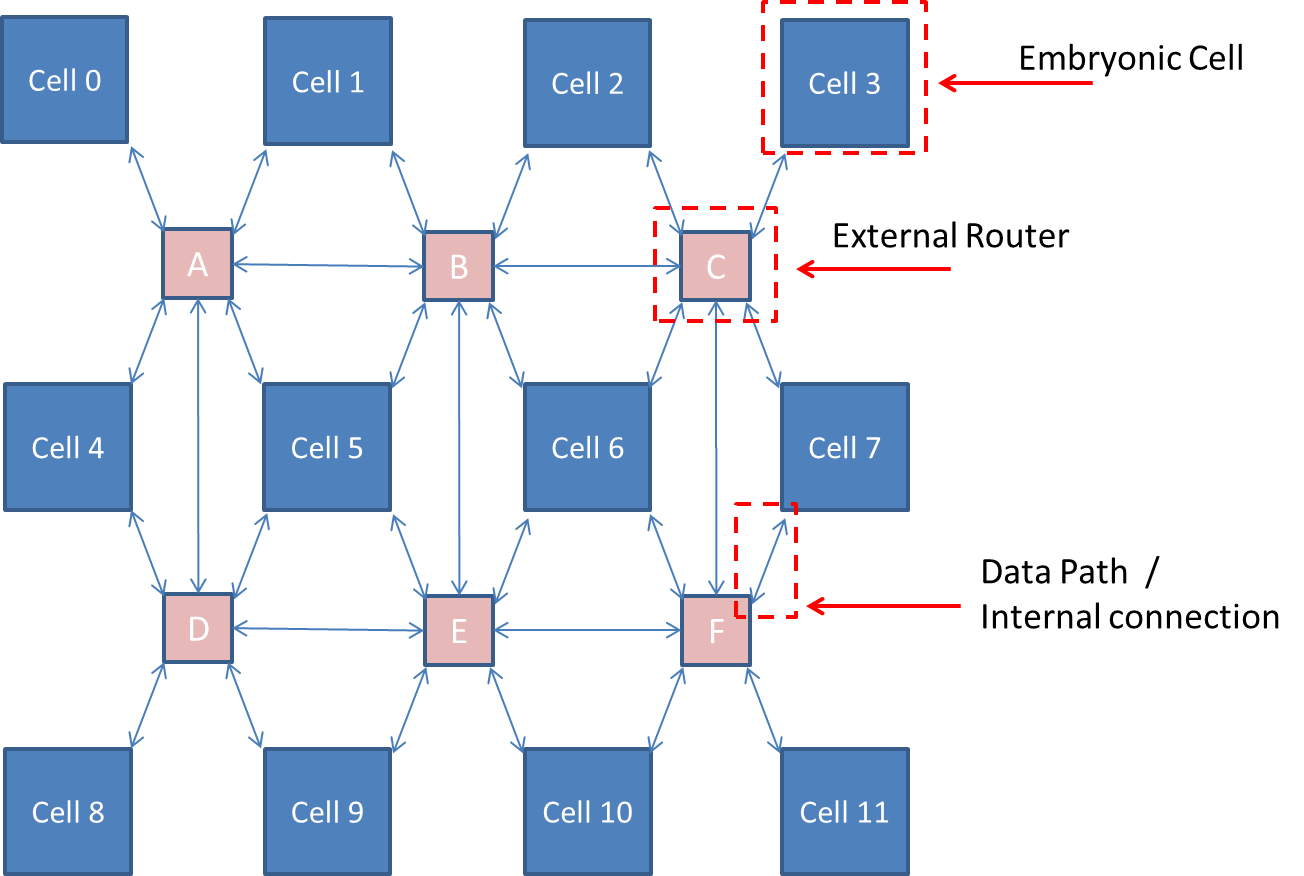

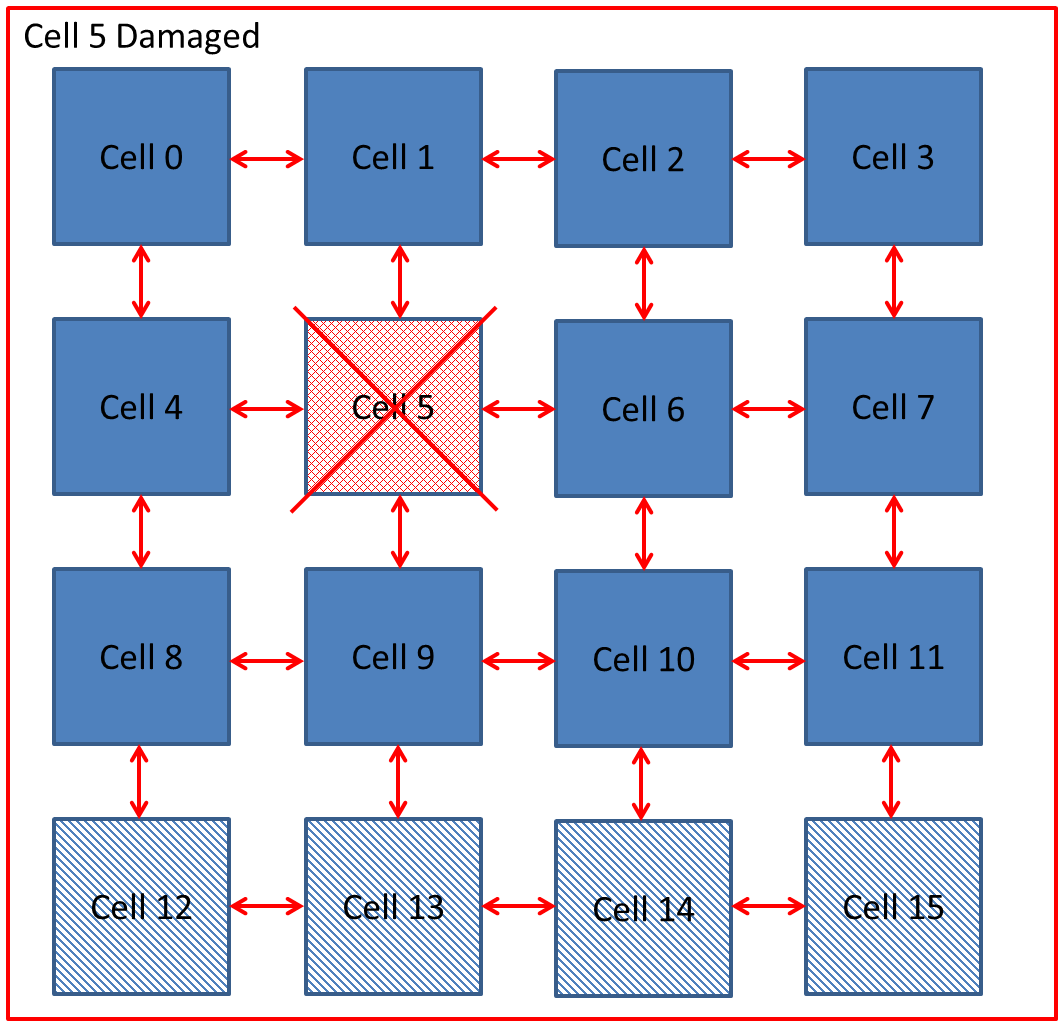

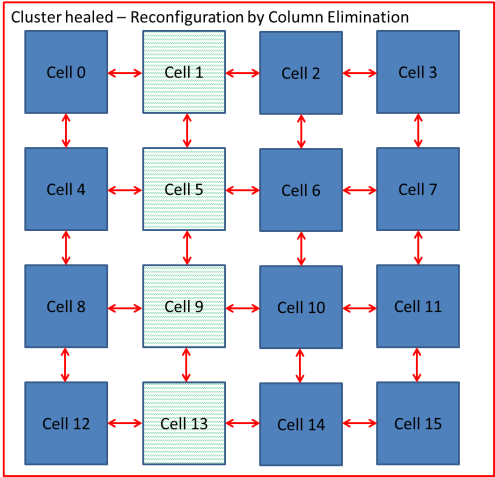

If a faulty cell in the FPGA is detected, a partial reconfiguration response is trigged. The aim is to allow a system to continue operating without being interrupted. There are three known methods of cell replacement which are Row / Column Elimination, Row & Column Elimination and Cell Elimination, each using a two dimensional array of logic elements

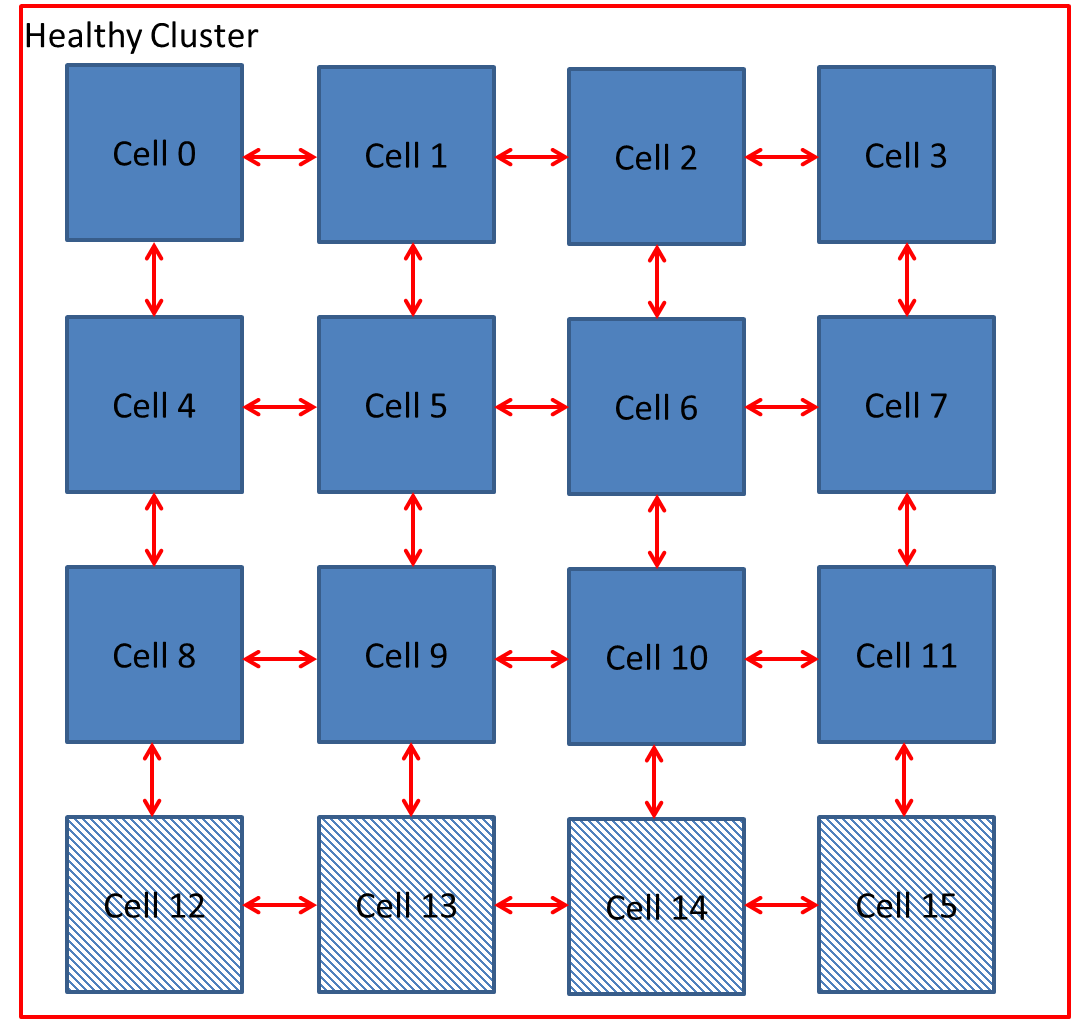

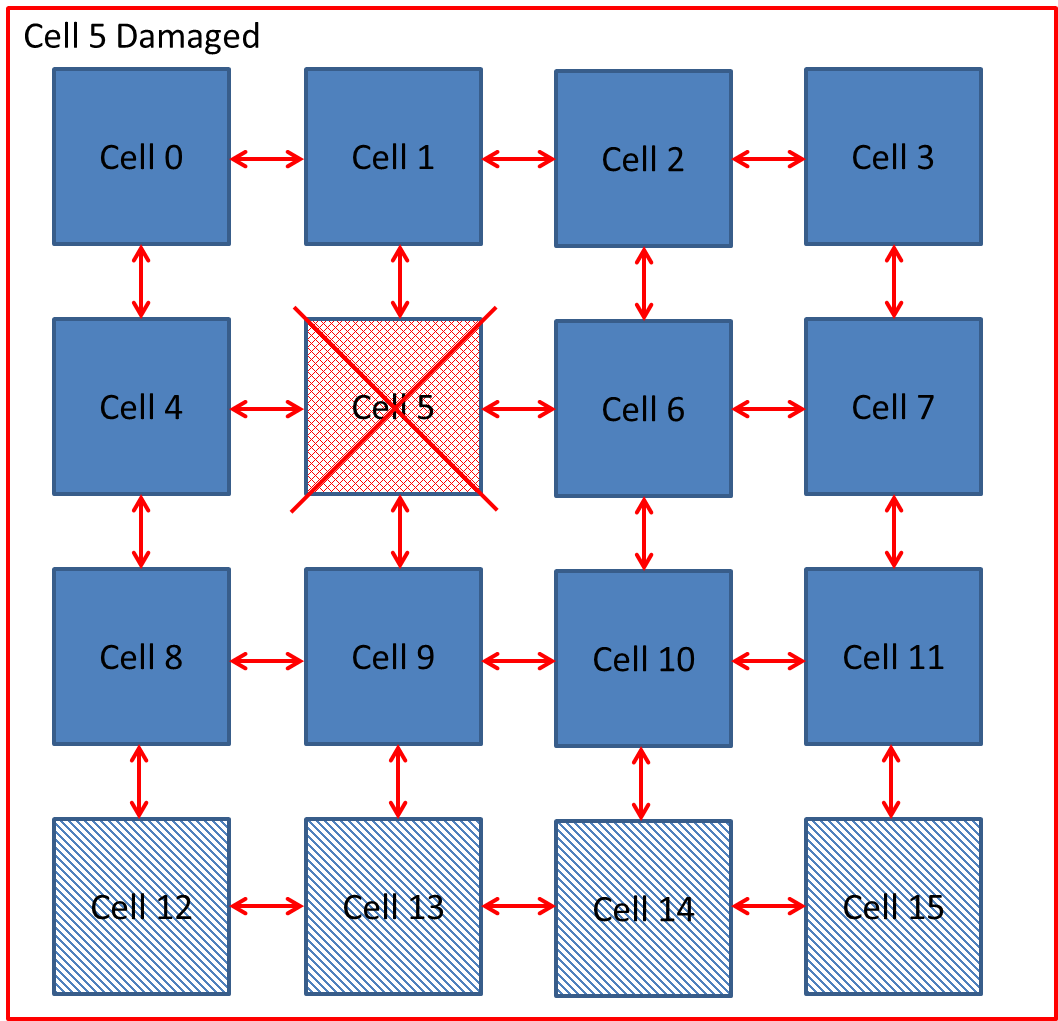

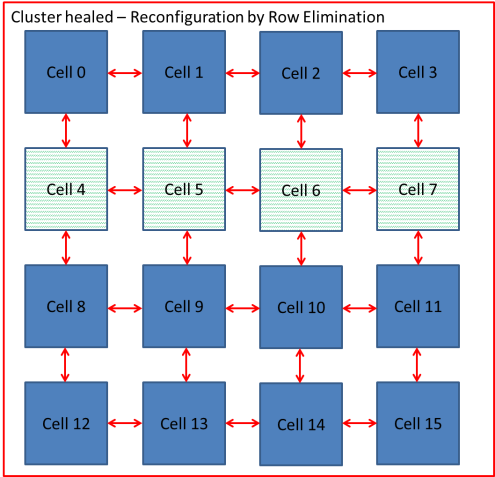

i) Row Elimination / Column Elimination. A failure of one cell causes the elimination of the entire row of interconnecting cells, this is demonstrated below in Figure 5‑4, Figure 5‑5, Figure 5‑6. The row is replaced by the row to the north until a spare cell is reached and the functional array is re-configured. Column Elimination uses similar methodology (42) and is demonstrated in Row-elimination was first proposed by Ortega et al (50) (51).

Figure ‑ Reconfiguration by Row Elimination

II) Row and Column Elimination. A failure of a cell will trigger a row or column elimination. However, if the cell does not correctly re-configure then row or column containing the cell will also be eliminated (42). Row and column elimination is used by Canham et al (52) (53).

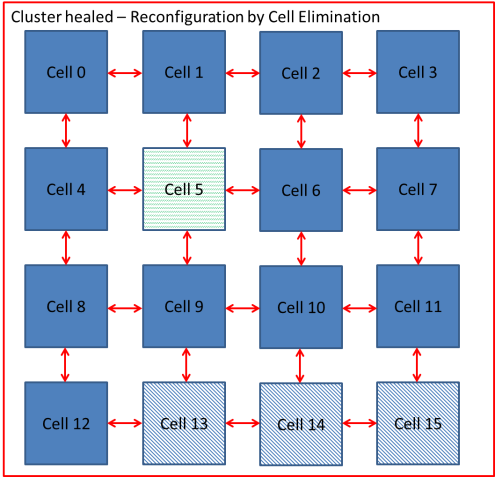

III) Cell Elimination. Faulty cells are replaced by spare cells to the right of the array. When they are no spare cells available, the row is eliminated. (42). Cell elimination for molecular repair was first proposed by Daniel Mange et al (54) (55).

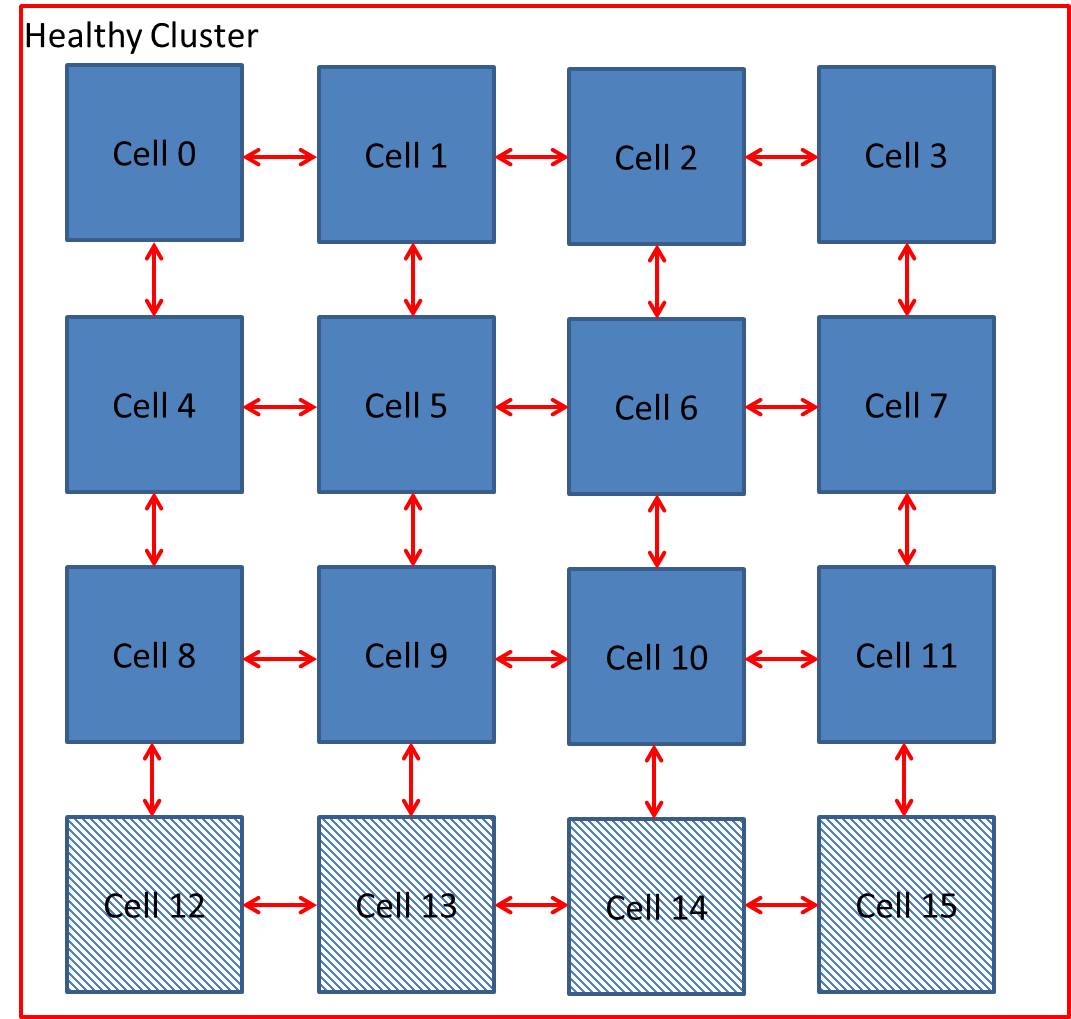

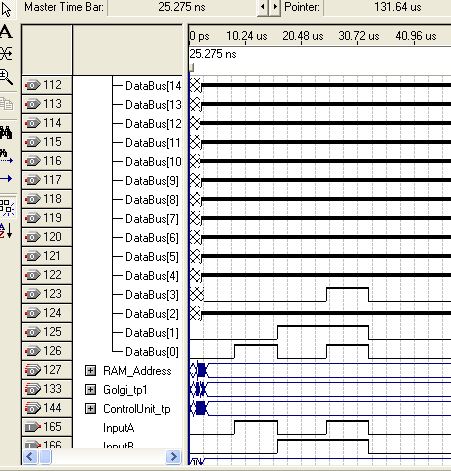

Xuegong focused on developing an embryotic cell which utilised row and column elimination. A more efficient method would be cell elimination, as only the defective cell would be removed as part of the reconfiguration process. This is demonstrated by a healthy cluster of cells shown in Figure 5‑7 and subsequently cell 5 fails in Figure 5‑8. The repair process works by taking cell 5 offline and replacing with spare cell 12 shown in Figure 5‑9. The reconfiguration process would need to ensure that data is routed to cell 12 automatically without loss of data. Also the cluster would need to perform the reconfiguration process without delaying the output response and therefore have Real-Time Fault Recovery.

Figure ‑ Reconfiguration by Cell Elimination

Multiply Clock Frequency

The first suggested method of temporal correctness is to operate the internal embryonic cluster at a clock frequency X times higher than the input / output system clock frequency. An example of an embryonic cell operating (hypothetically) 10x higher is shown in Figure 5‑10.

Figure ‑ Example of Embryonic Cell with higher clock freq

Providing the cells internal clock frequency is faster that the external clock frequency, it is feasible that any disruptions could be mitigated by hot-swapping faulty cells for spare cells (cluster reconfiguration) without impacting the temporal correctness. Hence the cluster would produce the output response within the expected time frame.

Cluster Configuration

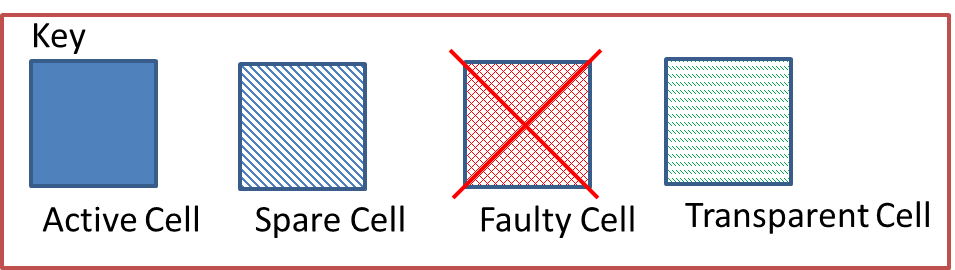

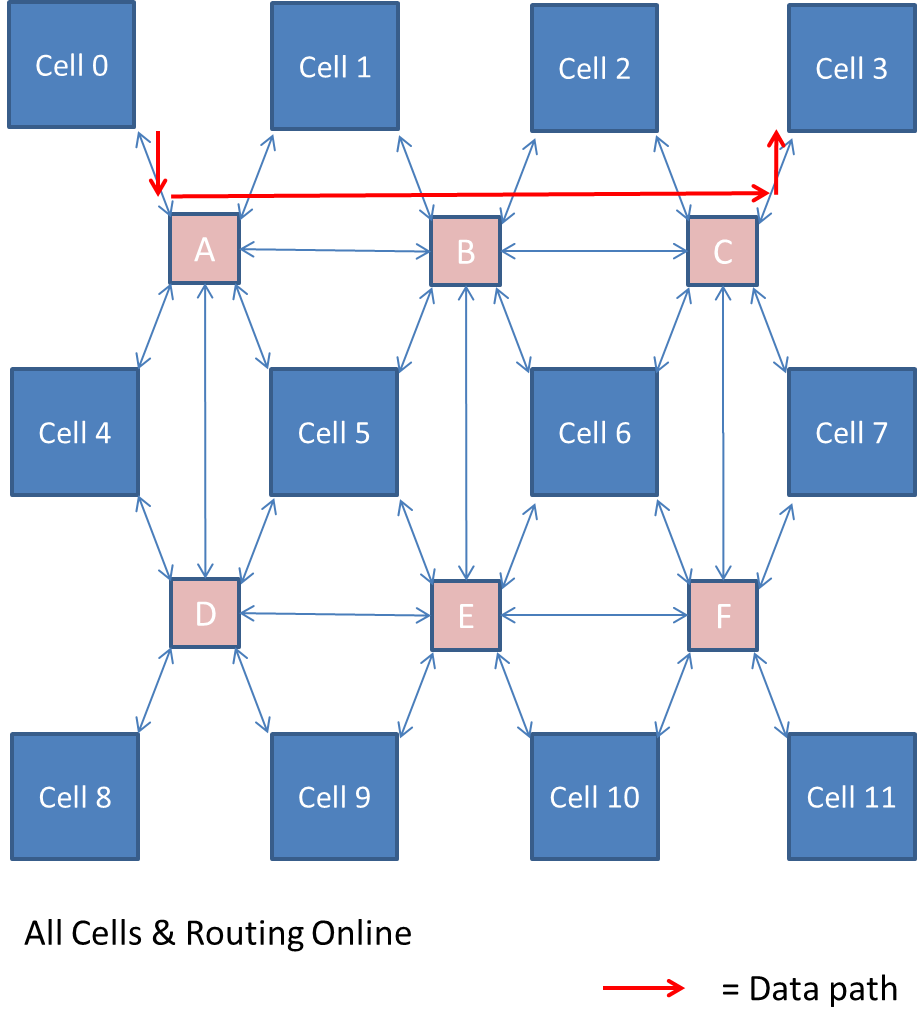

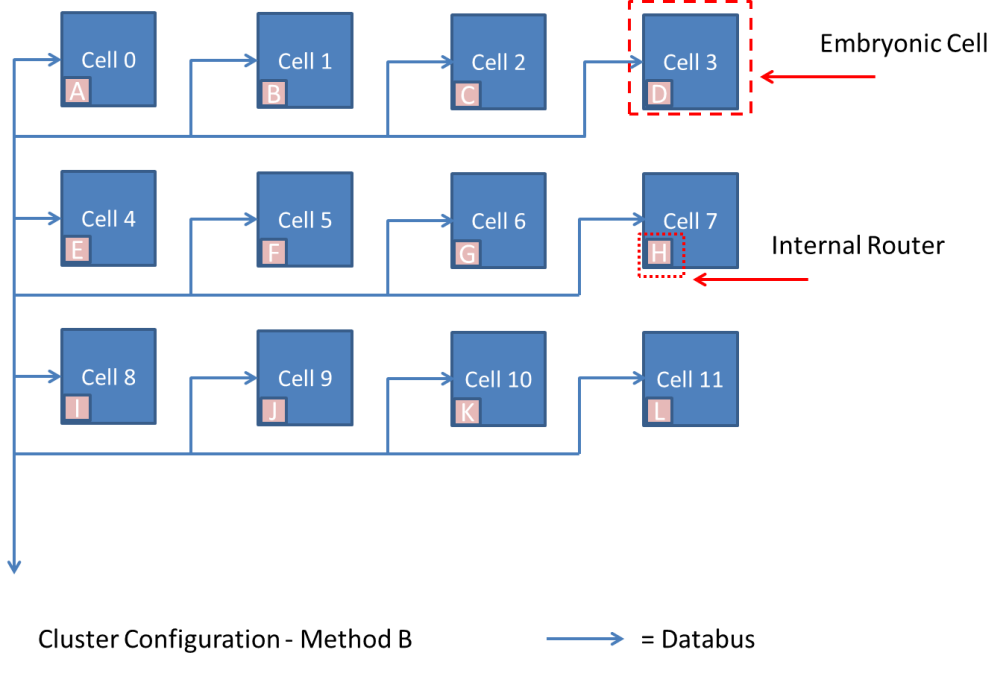

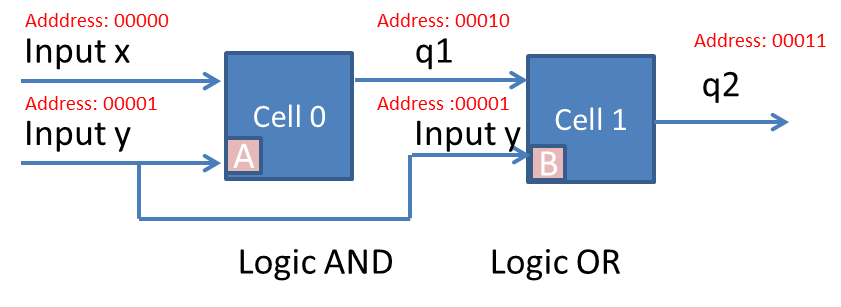

The biologically inspired design for this project consists of an array of embryonic cells, which shall be referred to as a cluster. Each of the embryonic cells within the cluster is identical in design and can perform any desired Boolean function. This is similar to stem cells in the human body which have the ability to perform any cellular function in the human body. A cluster of 12 cells are illustrated in Figure 5‑11.

Figure ‑ Cluster of 12 embryonic cells

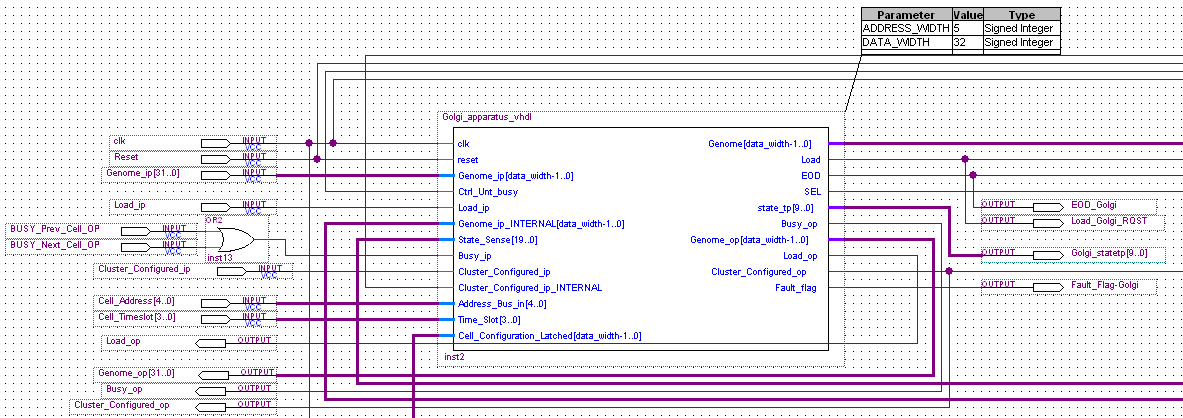

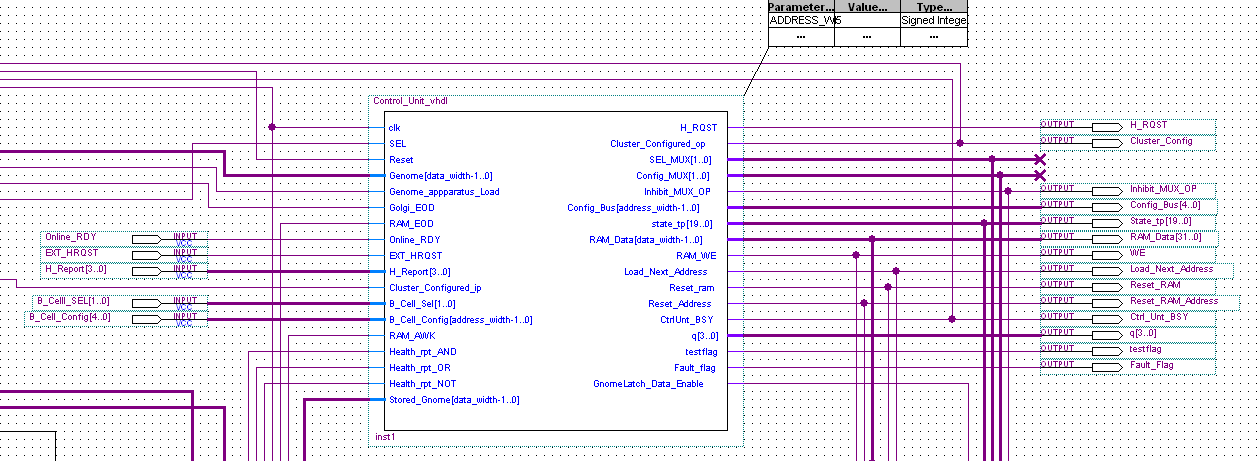

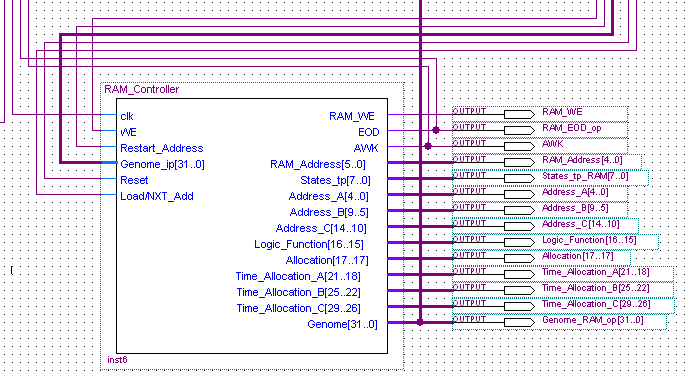

Each embryonic cell contains

- Router. This controls the flow of data to and fro the cell, similar to the Golgi Apparatus (Further information about the Golgi Apparatus can be found in Appendix C.4)

- RAM & RAM Controller. This is the cells memory and defines cells function, similar to DNA

- Control Unit. Controls how all the above mechanisms interact

The author has considered two main cluster configurations to transfer data between embryonic cells which were Method A and Method B, which is discussed next.

Cluster Configuration – Method A

Initially the cluster was going to have the external routers connected in a STAR configuration. This would result in each router being connected to four adjacent cells and up to four adjacent routers. Therefore, a 12-cell cluster would require 6 routers, as shown in Figure 5‑12, and a 32-cell cluster would require 21 routers.

Figure ‑ Cluster Configuration – Method A

A comparison of how many routers is required if the routers are internal or external to the cell, and the results are plotted in Figure 5‑13. This should that less routers are required when they are external to the cell.

Figure ‑ Method A: Number Cells vs Routers Relationship

If a router was damaged, then data would need to be routed through another data path / internal connection. For example, using Figure 5‑12, if we needed to send data from Cell 0 to Cell 9, the data could be routed through routers A->D. or A->B->E. Analysis of the diagram shows that each router could require up to 7 internal connections between cells. A 32-cell cluster would mean each router would require up to 8 internal connections.

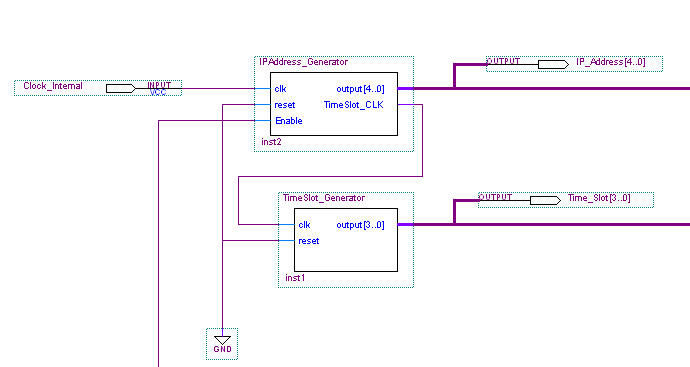

Each of these internal connections would be bidirectional. The router would be designated its own IP address and would have the destination IP address. Before the data is sent a packet is transmitted to configure a virtual path. Each router would contain a routing table of connected routers and their status, defining whether they are online or offline. The routing table is broadcasted to other routers in the cluster. Thus each router would know the status of the other routers. If the condition of a router changes or a cell changes status ie enters repair mode, then the routing table is updated and the table is re-broadcasted to the other routers maintaining data freshness.

The routing table could be designed to use the Dijkstra’s algorithm or Link state vector algorithm. A scenario could be that we need to connect cell 1 -> 3. This can be achieved using a route of A->B->C. However, if router B went offline, then an alternative route could be A-> D->E->F->C. A cluster of 12 cells are shown in Figure 5‑14.

Damaged Cell B taken offline

Figure ‑ Illustration of Router B Offline

Routing Table

Each of the cells can be switch online or offline independently. An online cell can process data and product a logic output response. An offline cell will not process data, and its output inhibited.

The routing table, shown in Table 5‑2, was designed to identify which cells are online (Logic 1) and which are off-line (logic 0). The top row shows the Router A to U, which are the 21 routers detailed previously. The table also shows 32 cells in the rows from Cell 0 to Cell 31.

Three different address structures were considered, and they are shown in Table 5‑2. IP address method Alpha uses 6 digits for an X coordinate and 6 digits for a Y coordinate. Each cell increments both X and Y and results in a 12-bit address. This was considered to be an inefficient use of address bits.

Next IP address method Beta was considered. However, this also uses a 12 bit address and was also considered inefficient in term of bits used.

IP Address Method Zeta was then considered which uses Grey Coding. This has the advantage of reducing the address to 6-bits and since the address only changes by 1-bit between adjacent cells there is the potential for error checking.

If the matrix shows an empty field, then Router and Cell are not connected. A Logic 1 in the matrix means the Router and the Cell are connected. For example Router A is connected to Cell 0, 1, 4 & 5.

If Router A went offline due to a failure, then the matrix would be updated such that the Column to Router A was changed from Logic 1 to Logic 0 (Figure 5‑11). If Cell 5 developed a fault, then the Row representing Cell 5 would be updated from Logic 1 to Logic 0 (Figure 5‑12).

This method raises two concerns. Firstly, as the number of cells increase, the number of interconnecting routes between embryonic cells increases exponentially as shown in Figure 5‑15.

Secondly, since the cells and routers are independent there is the potential for either to fail. A router failure could potentially result in a severed connection to healthy cells, and this would cause both router(s) and cell(s) to be taken offline. Therefore, Method B was developed to create a more efficient approach.

Figure ‑ Number of interconnecting signals

|

IP Address method Alpha |

IP Address method Beta |

IP Address Method Zeta (Grey code) |

|

Router |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

X |

Y |

Whole Address |

Path 1 |

Path 2 |

Path 3 |

Path 4 |

x |

y |

Bin X |

Bin Y |

IP Address |

x |

y |

Grey X |

Grey Y |

IP Address |

Cell |

A |

B |

C |

D |

E |

F |

G |

H |

I |

J |

K |

L |

M |

N |

O |

P |

Q |

R |

S |

T |

U |

|

000000 |

000000 |

000000000000 |

0 |

0 |

000000 |

000000 |

000000000000 |

0 |

0 |

000 |

000 |

000000 |

0 |

1 |

||||||||||||||||||||||||

|

000001 |

000001 |

000001000001 |

AB |

1 |

0 |

000001 |

000000 |

000001000000 |

1 |

0 |

001 |

000 |

001000 |

1 |

1 |

1 |

||||||||||||||||||||||

|

000010 |

000010 |

000010000010 |

BC |

2 |

0 |

000010 |

000000 |

000010000000 |

2 |

0 |

011 |

000 |

011000 |

2 |

1 |

1 |

||||||||||||||||||||||

|

000011 |

000011 |

000011000011 |

3 |

0 |

000011 |

000000 |

000011000000 |

3 |

0 |

010 |

000 |

010000 |

3 |

1 |

||||||||||||||||||||||||

|

000100 |

000100 |

000100000100 |

AD |

0 |

1 |

000000 |

000001 |

000000000001 |

0 |

1 |

000 |

001 |

000001 |

4 |

1 |

1 |

||||||||||||||||||||||

|

000101 |

000101 |

000101000101 |

DE |

AD |

BE |

1 |

1 |

000001 |

000001 |

000001000001 |

1 |

1 |

001 |

001 |

001001 |

5 |

1 |

1 |

1 |

1 |

||||||||||||||||||

|

000110 |

000110 |

000110000110 |

EF |

BE |

CF |

2 |

1 |

000010 |

000001 |

000010000001 |

2 |

1 |

011 |

001 |

011001 |

6 |

1 |

1 |

1 |

1 |

||||||||||||||||||

|

000111 |

000111 |

000111000111 |

CF |

3 |

1 |

000011 |

000001 |

000011000001 |

3 |

1 |

010 |

001 |

010001 |

7 |

1 |

1 |

||||||||||||||||||||||

|

001000 |

001000 |

001000001000 |

DG |

0 |

2 |

000000 |

000010 |

000000000010 |

0 |

2 |

000 |

011 |

000011 |

8 |

1 |

1 |

||||||||||||||||||||||

|

001001 |

001001 |

001001001001 |

GH |

DG |

EH |

1 |

2 |

000001 |

000010 |

000001000010 |

1 |

2 |

001 |

011 |

001011 |

9 |

1 |

1 |

1 |

1 |

||||||||||||||||||

|

001010 |

001010 |

001010001010 |

HI |

EH |

FI |

2 |

2 |

000010 |

000010 |

000010000010 |

2 |

2 |

011 |

011 |

011011 |

10 |

1 |

1 |

1 |

1 |

||||||||||||||||||

|

001011 |

001011 |

001011001011 |

FI |

3 |

2 |

000011 |

000010 |

000011000010 |

3 |

2 |

010 |

011 |

010011 |

11 |

1 |

1 |

||||||||||||||||||||||

|

001100 |

001100 |

001100001100 |

GJ |

0 |

3 |

000000 |

000011 |

000000000011 |

0 |

3 |

000 |

010 |

000010 |

12 |

1 |

1 |

||||||||||||||||||||||

|

001101 |

001101 |

001101001101 |

JK |

GJ |

HK |

1 |

3 |

000001 |

000011 |

000001000011 |

1 |

3 |

001 |

010 |

001010 |

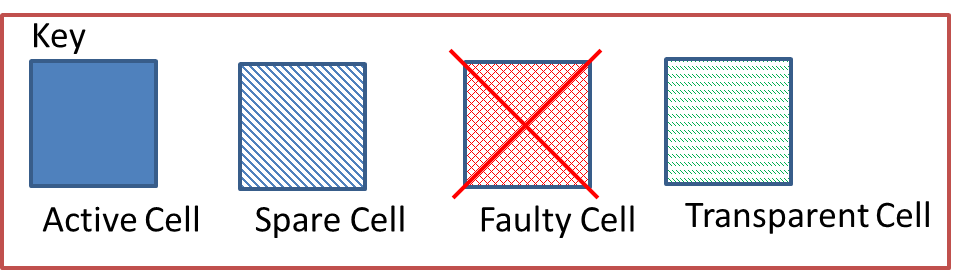

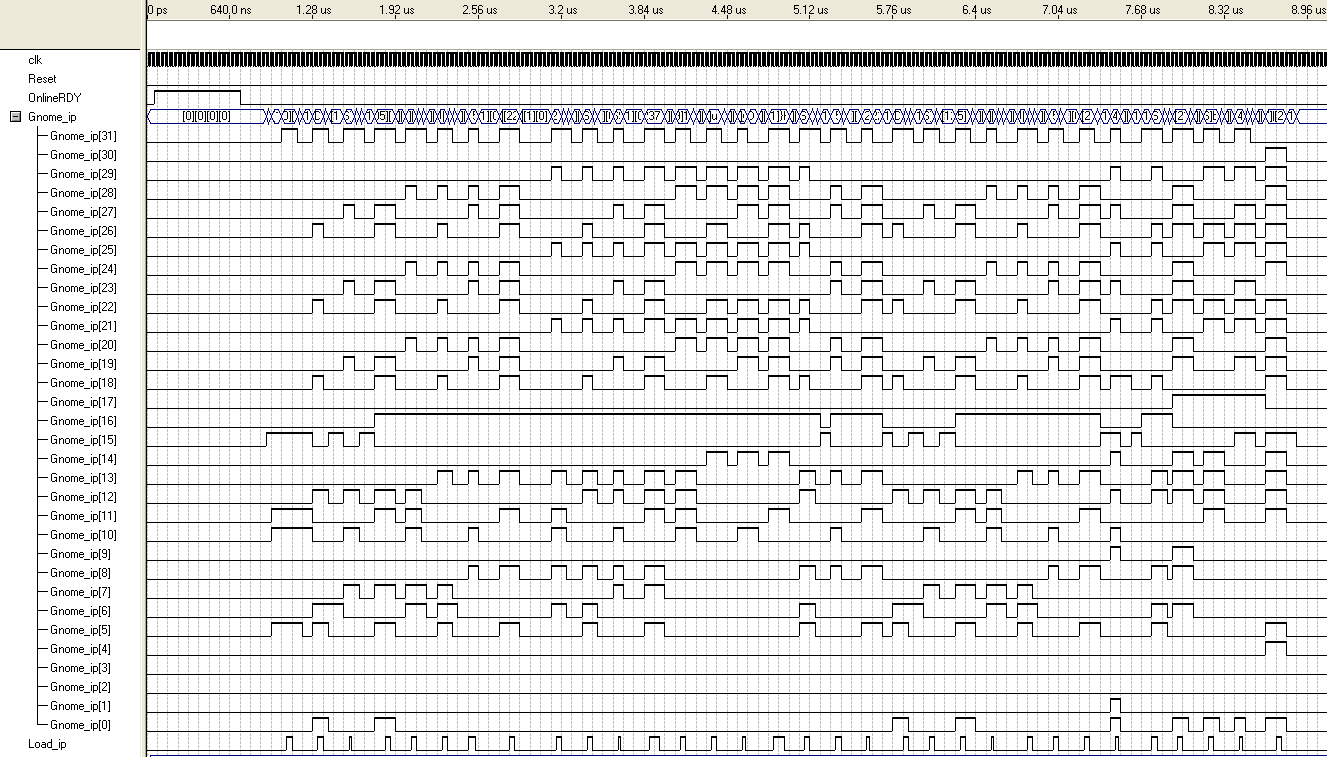

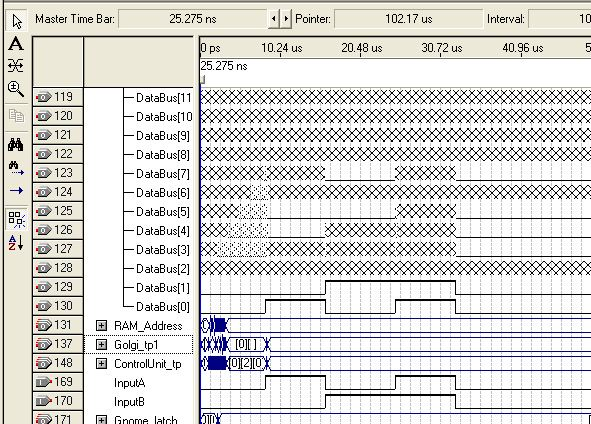

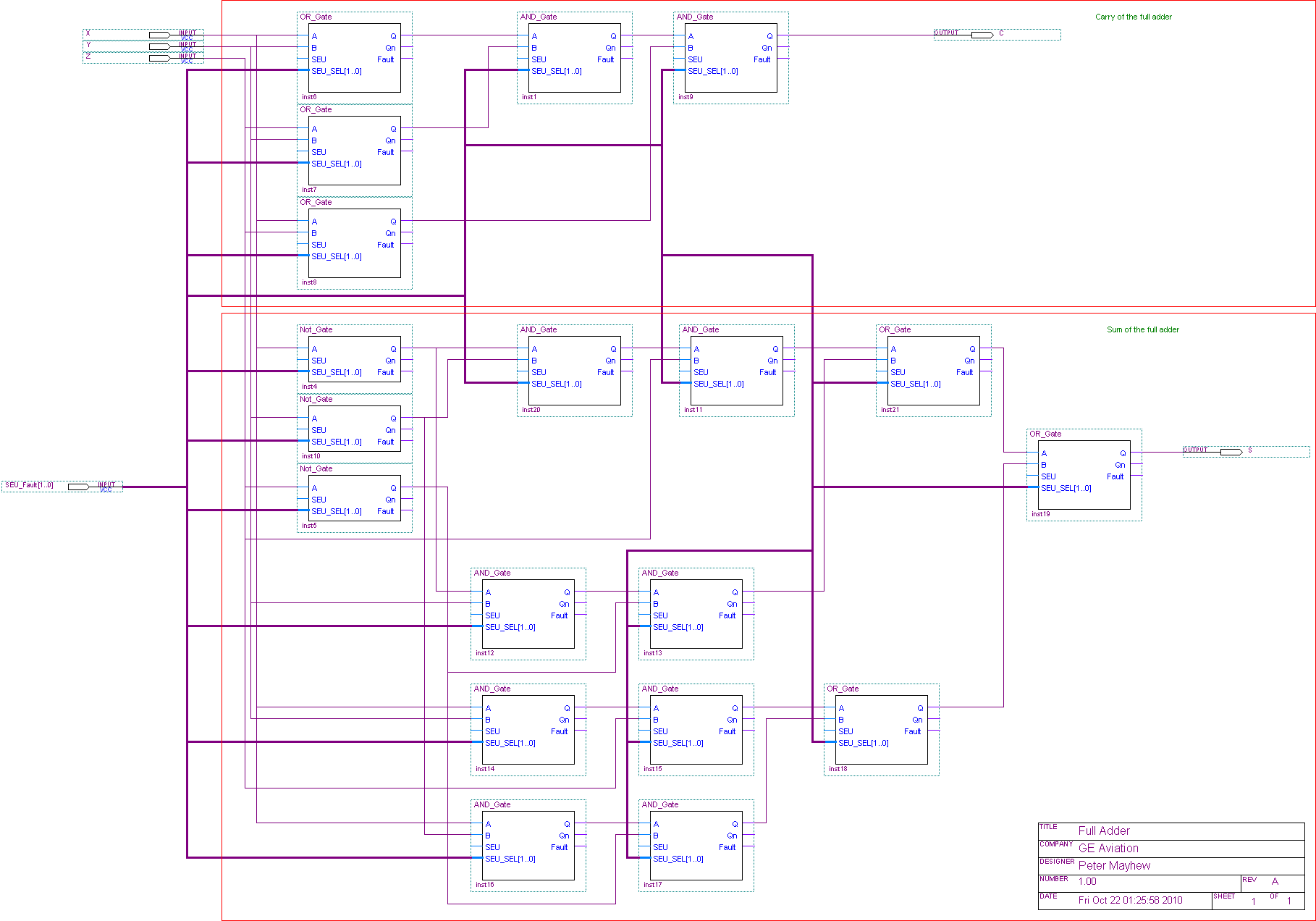

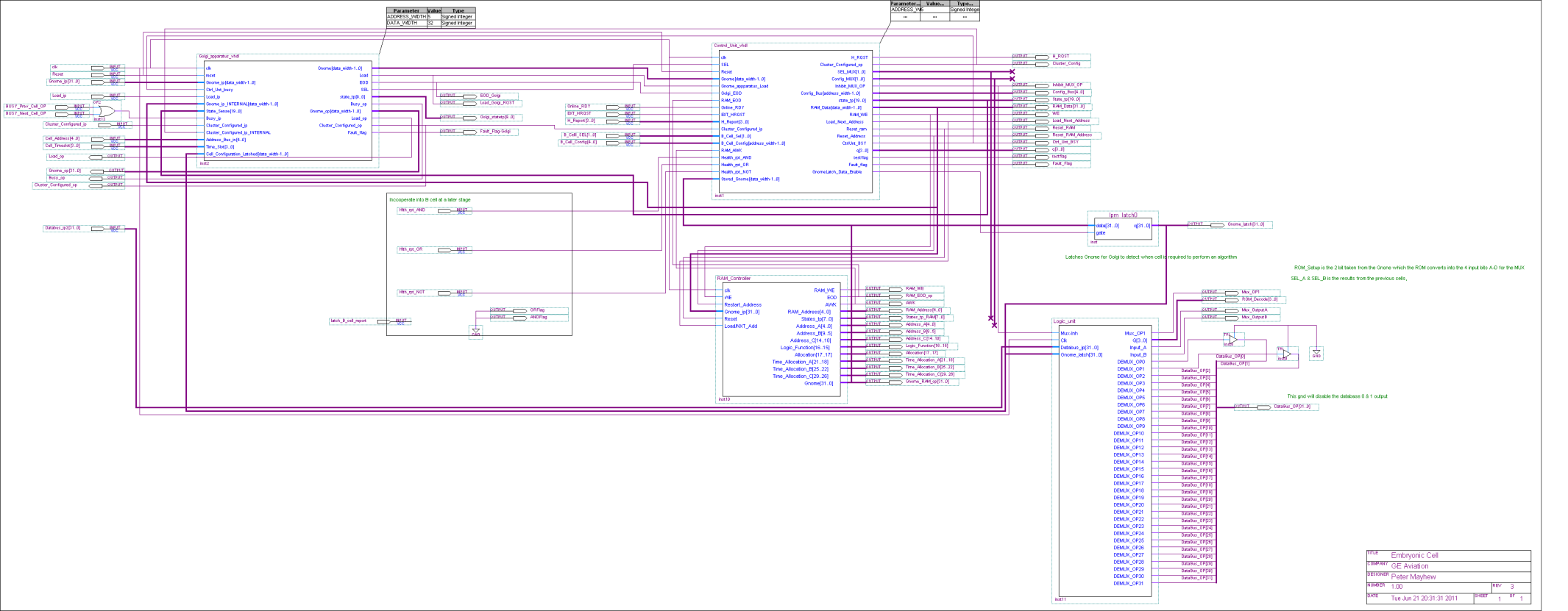

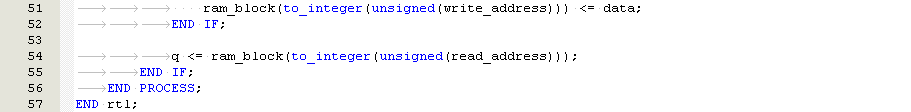

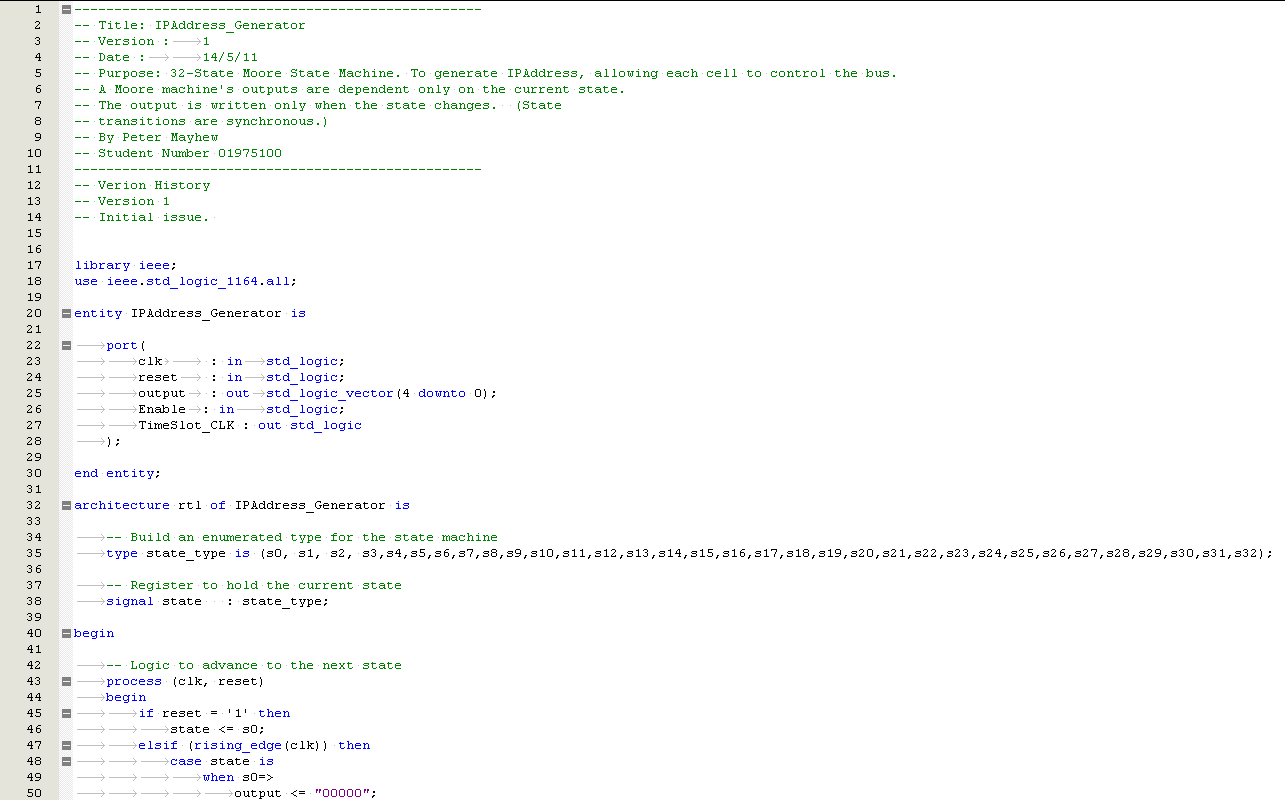

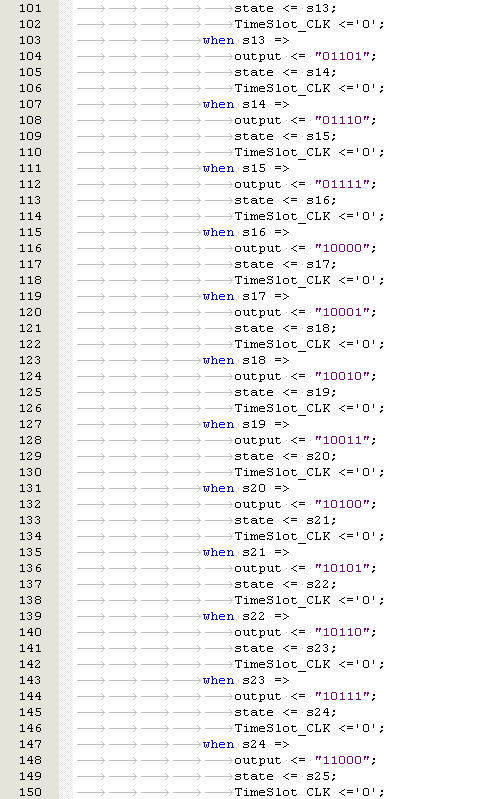

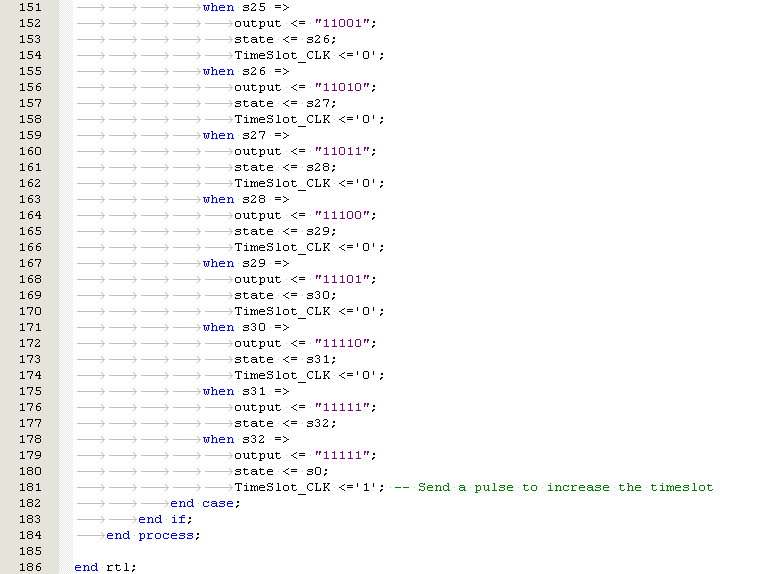

13 |